# JEDEC STANDARD

**Serial Flash Discoverable Parameters** (**SFDP**)

**JESD216D** (Revision of JESD216C, August 2018)

NOVEMBER 2018

JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

#### NOTICE

JEDEC standards and publications contain material that has been prepared, reviewed, and approved through the JEDEC Board of Directors level and subsequently reviewed and approved by the JEDEC legal counsel.

JEDEC standards and publications are designed to serve the public interest through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than JEDEC members, whether the standard is to be used either domestically or internationally.

JEDEC standards and publications are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action JEDEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the JEDEC standards or publications.

The information included in JEDEC standards and publications represents a sound approach to product specification and application, principally from the solid state device manufacturer viewpoint. Within the JEDEC organization there are procedures whereby a JEDEC standard or publication may be further processed and ultimately become an ANSI standard.

No claims to be in conformance with this standard may be made unless all requirements stated in the standard are met.

Inquiries, comments, and suggestions relative to the content of this JEDEC standard or publication should be addressed to JEDEC at the address below, or refer to <u>www.jedec.org</u> under Standards and Documents for alternative contact information.

Published by ©JEDEC Solid State Technology Association 2018 3103 North 10th Street Suite 240 South Arlington, VA 22201-2108

JEDEC retains the copyright on this material. By downloading this file the individual agrees not to charge for or resell the resulting material.

#### **PRICE: Contact JEDEC**

Printed in the U.S.A. All rights reserved

Downloaded by daniel kung (gyd0317@gmail.com) on Dec 27, 2018, 6:12 am PST

#### PLEASE!

#### DON'T VIOLATE THE LAW!

This document is copyrighted by JEDEC and may not be reproduced without permission.

For information, contact:

JEDEC Solid State Technology Association 3103 North 10th Street Suite 240 South Arlington, VA 22201-2107

or refer to www.jedec.org under Standards-Documents/Copyright Information.

Downloaded by daniel kung (gyd0317@gmail.com) on Dec 27, 2018, 6:12 am PST

# SERIAL FLASH DISCOVERABLE PARAMETERS (SFDP) STANDARD

| Contents |  |

|----------|--|

| Contents |  |

|         |                                          | Page |

|---------|------------------------------------------|------|

| Forewo  | rd                                       | viii |

| Introdu | ction                                    | viii |

| 1       | Scope                                    | 1    |

| 2       | Normative reference                      | 1    |

| 3       | Terms and definitions                    | 2    |

| 4       | Read SFDP Command Protocol               | 3    |

| 4.1     | Instruction                              | 3    |

| 4.2     | Address                                  | 3    |

| 4.3     | Wait States                              | 4    |

| 4.4     | Clock Rate                               | 4    |

| 4.5     | Command Modes                            | 4    |

| 4.5.1   | Read SFDP (1-1-1) Mode                   | 5    |

| 4.5.2   | Read SFDP (2-2-2) Mode                   | 6    |

| 4.5.3   | Read SFDP (4S-4S-4S) Mode                | 6    |

| 4.5.4   | Read SFDP (4S-4D-4D) Mode                | 7    |

| 4.5.5   | Read SFDP (8D-8D-8D) Mode                | 7    |

| 4.5.6   | Fetch SFDP (1-1-1) Mode                  | 8    |

| 4.5.7   | Fetch SFDP (2-2-2) Mode                  | 8    |

| 4.5.8   | Fetch SFDP (4S-4S-4S and 4S-4D-4D) Mode  | 9    |

| 4.5.9   | Fetch SFDP (8D-8D-8D) Mode               | 9    |

| 5       | Read SFDP Behavior                       | 10   |

| 5.1     | Security                                 | 10   |

| 5.2     | Reset and Hold Functions                 | 10   |

| 5.3     | Read Wrap                                | 10   |

| 5.4     | SFDP Address Boundary Wrap               | 10   |

| 5.5     | Reserved SFDP Locations                  | 10   |

| 6       | SFDP Database                            | 11   |

| 6.1     | SFDP Header Structure                    | 11   |

| 6.2     | SFDP Header                              | 12   |

| 6.2.1   | SFDP Header: 1 <sup>st</sup> DWORD       | 12   |

| 6.2.2   | SFDP Header: 2 <sup>nd</sup> DWORD       | 13   |

| 6.2.3   | Definition of SFDP Access Protocol Field | 14   |

| 6.3     | Parameter Headers                        | 19   |

| 6.3.1   | Parameter Header: 1 <sup>st</sup> DWORD  | 19   |

| 6.3.2   | Parameter Header: 2 <sup>nd</sup> DWORD  | 19   |

| 6.3.3   | Definition of Parameter ID Field         | 20   |

| 6.3.4  | Example SFDP Headers                                               | .22 |

|--------|--------------------------------------------------------------------|-----|

| 6.4    | JEDEC Basic Flash Parameter Header and Table                       | .24 |

| 6.4.1  | JEDEC Basic Flash Parameter Header: 1st DWORD                      | .24 |

| 6.4.2  | JEDEC Basic Flash Parameter Header: 2nd DWORD                      | .25 |

| 6.4.3  | JEDEC Basic Flash Parameter Table Overview                         | .25 |

| 6.4.4  | JEDEC Basic Flash Parameter Table: 1st DWORD                       | .26 |

| 6.4.5  | JEDEC Basic Flash Parameter Table: 2 <sup>nd</sup> DWORD           | .28 |

| 6.4.6  | JEDEC Basic Flash Parameter Table: 3 <sup>rd</sup> DWORD           | .28 |

| 6.4.7  | JEDEC Basic Flash Parameter Table: 4 <sup>th</sup> DWORD           | .29 |

| 6.4.8  | JEDEC Basic Flash Parameter Table: 5 <sup>th</sup> DWORD           | .30 |

| 6.4.9  | JEDEC Basic Flash Parameter Table: 6 <sup>th</sup> DWORD           | .30 |

| 6.4.10 | JEDEC Basic Flash Parameter Table: 7 <sup>th</sup> DWORD           | .31 |

| 6.4.11 | JEDEC Basic Flash Parameter Table: 8 <sup>th</sup> DWORD           | .31 |

| 6.4.12 | JEDEC Basic Flash Parameter Table: 9 <sup>th</sup> DWORD           | .32 |

| 6.4.13 | JEDEC Basic Flash Parameter Table: 10 <sup>th</sup> DWORD          | .32 |

| 6.4.14 | JEDEC Basic Flash Parameter Table: 11 <sup>th</sup> DWORD          | .34 |

| 6.4.15 | JEDEC Basic Flash Parameter Table: 12 <sup>th</sup> DWORD          | .36 |

| 6.4.16 | JEDEC Basic Flash Parameter Table: 13 <sup>th</sup> DWORD          | .38 |

| 6.4.17 | JEDEC Basic Flash Parameter Table: 14 <sup>th</sup> DWORD          | .39 |

| 6.4.18 | JEDEC Basic Flash Parameter Table: 15 <sup>th</sup> DWORD          | .40 |

| 6.4.19 | JEDEC Basic Flash Parameter Table: 16 <sup>th</sup> DWORD          | .42 |

| 6.4.20 | JEDEC Basic Flash Parameter Table: 17th DWORD                      | .44 |

| 6.4.21 | JEDEC Basic Flash Parameter Table: 18 <sup>th</sup> DWORD          | .45 |

| 6.4.22 | JEDEC Basic Flash Parameter Table: 19 <sup>th</sup> DWORD          | .48 |

| 6.4.23 | JEDEC Basic Flash Parameter Table: 20 <sup>th</sup> DWORD          | .49 |

| 6.5    | JEDEC Sector Map Parameter Header and Table                        | .53 |

| 6.5.1  | Sector Map Parameter Header: 1 <sup>st</sup> DWORD                 | .54 |

| 6.5.2  | Sector Map Parameter Header: 2 <sup>nd</sup> DWORD                 | .54 |

| 6.5.3  | Configuration Detection Command Descriptor, 1st DWORD              | .56 |

| 6.5.4  | Configuration Detection Command Descriptor, 2 <sup>nd</sup> DWORD  | .57 |

| 6.5.5  | Configuration Map Descriptor Header DWORD                          | .58 |

| 6.5.6  | Region DWORD                                                       | .58 |

| 6.5.7  | Sector Map Parameter Table – Example 1                             | .60 |

| 6.5.8  | Sector Map Parameter Table – Example 2                             | .63 |

| 6.6    | JEDEC 4-byte Address Instruction Parameter Header and Table        | .64 |

| 6.6.1  | 4-byte Address Instruction Parameter Header: 1 <sup>st</sup> DWORD | .64 |

| 6.6.2  | 4-byte Address Instruction Parameter Header: 2 <sup>nd</sup> DWORD | .64 |

| 6.6.3  | 4-byte Address Instuction Table, 1 <sup>st</sup> DWORD             | .65 |

| 6.6.4  | 4-byte Address Instuction Table, 2 <sup>nd</sup> DWORD             | .68 |

| 6.7    | JEDEC eXtended Serial Peripheral Interface (xSPI) Profile 1.0 Parameter Header and Table                                                                            | .69 |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.7.1  | JEDEC xSPI (Profile 1.0) Parameter Header: 1 <sup>st</sup> DWORD                                                                                                    | .69 |

| 6.7.2  | JEDEC xSPI (Profile 1.0) Parameter Header: 2 <sup>nd</sup> DWORD                                                                                                    | .69 |

| 6.7.3  | JEDEC xSPI (Profile 1.0) Parameter Table: 1 <sup>st</sup> DWORD - Command Codes used in 8D-8D-8D protocol mode                                                      |     |

| 6.7.4  | JEDEC xSPI (Profile 1.0) Parameter Table: 2 <sup>nd</sup> DWORD - Command Codes used in 8D-8D-8D protocol mode                                                      |     |

| 6.7.5  | JEDEC xSPI (Profile 1.0) Parameter Table: 3 <sup>rd</sup> DWORD - Memory Commands Supported in 8D-8D-8D protocol mode                                               |     |

| 6.7.6  | JEDEC xSPI (Profile 1.0) Parameter Table: 4 <sup>th</sup> DWORD - Dummy cycles used for various frequencies                                                         | .73 |

| 6.7.7  | JEDEC xSPI (Profile 1.0) Parameter Table: 5th DWORD - Dummy cycles used for various frequencies                                                                     | .73 |

| 6.8    | JEDEC eXtended Serial Peripheral Interface (xSPI) - Profile 2.0 Parameter Header and Table                                                                          | .74 |

| 6.8.1  | JEDEC xSPI (Profile 2.0) Parameter Header: 1 <sup>st</sup> DWORD                                                                                                    | .74 |

| 6.8.2  | JEDEC xSPI (Profile 2.0) Parameter Header: 2 <sup>nd</sup> DWORD                                                                                                    | .74 |

| 6.8.3  | JEDEC xSPI (Profile 2.0) Parameter Table: 1 <sup>st</sup> DWORD - Command Codes used in 8D-8D-8D Profile 2 protocol mode                                            |     |

| 6.8.4  | JEDEC xSPI (Profile 2.0) Parameter Table: 2 <sup>nd</sup> DWORD - Dummy cycles used for various frequencies                                                         | .76 |

| 6.8.5  | JEDEC xSPI (Profile 2.0) Parameter Table: 3rd DWORD - Dummy cycles used for various frequencies                                                                     | .77 |

| 6.9    | Status, Control and Configuration Register Map for SPI Memory Devices                                                                                               | .77 |

| 6.9.1  | SCCR Map for SPI Memory Devices Parameter Header: 1st DWORD                                                                                                         | .78 |

| 6.9.2  | SCCR Map for SPI Memory Devices Parameter Header: 2 <sup>nd</sup> DWORD                                                                                             | .79 |

| 6.9.3  | SCCR Map for SPI Memory Devices Parameter Table: 1st DWORD – Volatile registers address offset                                                                      | .79 |

| 6.9.4  | SCCR Map for SPI Memory Devices Parameter Table: 2 <sup>nd</sup> DWORD – Non-Volatile registers address of                                                          |     |

| 6.9.5  | SCCR Map for SPI Memory Devices Parameter Table: 3 <sup>rd</sup> DWORD – Generic Addressable Read/Write Status/Control register commands for volatile registers     | .80 |

| 6.9.6  | SCCR Map for SPI Memory Devices Parameter Table: 4 <sup>th</sup> DWORD – Generic Addressable Read/Write Status/Control register commands for non-volatile registers | .81 |

| 6.9.7  | SCCR Map for SPI Memory Devices Parameter Table: 5th DWORD – WIP (Required for xSPI)                                                                                | .82 |

| 6.9.8  | SCCR Map for SPI Memory Devices Parameter Table: 6th DWORD – WEL                                                                                                    | .83 |

| 6.9.9  | SCCR Map for SPI Memory Devices Parameter Table: 7th DWORD – Program Error                                                                                          | .84 |

| 6.9.10 | SCCR Map for SPI Memory Devices Parameter Table: 8th DWORD – Erase Error                                                                                            | .85 |

| 6.9.11 | SCCR Map for SPI Memory Devices Parameter Table: 9 <sup>th</sup> DWORD – Variable Dummy Cycle Settings - Volatile Register                                          |     |

| 6.9.12 | SCCR Map for SPI Memory Devices Parameter Table: 10 <sup>th</sup> DWORD – Variable Dummy Cycle Settings<br>Non Volatile Register                                    |     |

| 6.9.13 | SCCR Map for SPI Memory Devices Parameter Table: 11 <sup>th</sup> DWORD – Variable Dummy Cycle Settings bit patterns                                                |     |

| 6.9.14 | SCCR Map for SPI Memory Devices Parameter Table: 12 <sup>th</sup> DWORD – Variable Dummy Cycle Settings bit patterns                                                |     |

| 6.9.15 | SCCR Map for SPI Memory Devices Parameter Table: 13 <sup>th</sup> DWORD – Variable Dummy Cycle Settings bit patterns                                                |     |

| 6.9.16 | SCCR Map for SPI Memory Devices Parameter Table: 14th DWORD – QPI Mode Enable Volatile                                                                              | .92 |

| 6.9.17  | SCCR Map for SPI Memory Devices Parameter Table: 15 <sup>th</sup> DWORD – QPI Mode Enable - Non Volatile93                                               |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.9.18  | SCCR Map for SPI Memory Devices Parameter Table: 16 <sup>th</sup> DWORD – Octal Mode Enable - Volatile94                                                 |

| 6.9.19  | SCCR Map for SPI Memory Devices Parameter Table: 17 <sup>th</sup> DWORD – Octal Mode Enable- Non-Volatile<br>                                            |

| 6.9.20  | SCCR Map for SPI Memory Devices Parameter Table: 18 <sup>th</sup> DWORD – STR or DTR mode select - Volatile                                              |

| 6.9.21  | SCCR Map for SPI Memory Devices Parameter Table: 19 <sup>th</sup> DWORD – STR or DTR mode select – Non<br>Volatile                                       |

| 6.9.22  | SCCR Map for SPI Memory Devices Parameter Table: 20 <sup>th</sup> DWORD – STR Octal Mode Enable - Volatile<br>                                           |

| 6.9.23  | SCCR Map for SPI Memory Devices Parameter Table: 21 <sup>st</sup> DWORD – STR Octal Mode Enable - Non-<br>Volatile                                       |

| 6.9.24  | SCCR Map for SPI Memory Devices Parameter Table: 22 <sup>nd</sup> DWORD – DTR Octal Mode Enable - Volatile                                               |

| 6.9.25  | SCCR Map for SPI Memory Devices Parameter Table: 23 <sup>rd</sup> DWORD – DTR Octal Mode Enable – Non-<br>Volatile                                       |

| 6.9.26  | SCCR Map for SPI Memory Devices Parameter Table: 24 <sup>th</sup> DWORD – DPD Status                                                                     |

| 6.9.27  | SCCR Map for SPI Memory Devices Parameter Table: 25 <sup>th</sup> DWORD – UDPD Status                                                                    |

| 6.9.28  | SCCR Map for SPI Memory Devices Parameter Table: 26 <sup>th</sup> DWORD – Output Driver Strength - Volatile                                              |

| 6.9.29  | SCCR Map for SPI Memory Devices Parameter Table: 27 <sup>th</sup> DWORD – Output Driver Strength – Non Volatile                                          |

| 6.9.30  | SCCR Map for SPI Memory Devices Parameter Table: 28 <sup>th</sup> DWORD – Output Driver Strength control bit patterns                                    |

| 6.10    | Status, Control and Configuration Register Map for xSPI Profile 2.0 Memory Devices                                                                       |

| 6.10.1  | SCCR Map for xSPI Profile 2.0 Memory Devices Parameter Header: 1st DWORD108                                                                              |

| 6.10.2  | SCCR Map for xSPI Profile 2.0 Memory Devices Parameter Header: 2 <sup>nd</sup> DWORD108                                                                  |

| 6.10.3  | SCCR Map for xSPI Profile 2.0 Memory Devices Parameter Table: 1 <sup>st</sup> DWORD – Volatile registers address offset                                  |

| 6.10.4  | SCCR Map for xSPI Profile 2.0 Memory Devices Parameter Table: 2 <sup>nd</sup> DWORD – Non-Volatile registers address offset                              |

| 6.10.5  | SCCR Map for xSPI Profile 2.0 Memory Devices Parameter Table: 3 <sup>rd</sup> DWORD – Generic Addressable<br>Read/Write Status/Control register commands |

| 6.10.6  | SCCR Map for xSPI Profile 2.0 Memory Devices Parameter Table: 4 <sup>th</sup> DWORD – Program Error110                                                   |

| 6.10.7  | SCCR Map for xSPI Profile 2.0 Memory Devices Parameter Table: 5th DWORD – Erase Error110                                                                 |

| 6.10.8  | SCCR Map for xSPI Profile 2.0 Memory Devices Parameter Table: 6 <sup>th</sup> DWORD – Variable Dummy Cycle<br>Settings – Volatile Register               |

| 6.10.9  | SCCR Map for xSPI Profile 2.0 Memory Devices Parameter Table: 7 <sup>th</sup> DWORD – Variable Dummy Cycle Settings- Non Volatile Register               |

| 6.10.10 | SCCR Map for xSPI Profile 2.0 Memory Devices Parameter Table: 8 <sup>th</sup> DWORD – Variable Dummy Cycle Settings – bit patterns                       |

| 6.10.11 | SCCR Map for xSPI Profile 2.0 Memory Devices Parameter Table: 9 <sup>th</sup> DWORD – Variable Dummy Cycle<br>Settings – bit patterns                    |

| 6.10.12 | SCCR Map for xSPI Profile 2.0 Memory Devices Parameter Table: 10 <sup>th</sup> DWORD – Variable Dummy<br>Cycle Settings – bit patterns                   |

|         |                                                                                                                                                          |

| 6.10.13 | SCCR Map for xSPI Profile 2.0 Memory Devices Parameter Table: 11 <sup>th</sup> DWORD – Output Driver Strength<br>- Volatile                        |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.10.14 | SCCR Map for xSPI Profile 2.0 Memory Devices Parameter Table: 12 <sup>th</sup> DWORD – Output Driver Strength – Non Volatile                       |

| 6.10.15 | SCCR Map for xSPI Profile 2.0 Memory Devices Parameter Table: 13 <sup>th</sup> DWORD – Output Driver Strength control bit patterns                 |

| 6.11    | Status, Control and Configuration Register Map Offsets for Multi-Chip SPI Memory Devices118                                                        |

| 6.11.1  | Status, Control and Configuration Register Map Parameter Header: 1st DWORD118                                                                      |

| 6.11.2  | Status, Control and Configuration Register Map Parameter Header: 2 <sup>nd</sup> DWORD                                                             |

| 6.11.3  | Status, Control and Configuration Register Map Parameter Table: 1 <sup>st</sup> DWORD – Volatile registers address offset for die 1                |

| 6.11.4  | Status, Control and Configuration Register Map Parameter Table: 2 <sup>nd</sup> DWORD – Non-Volatile registers address offset for die 1            |

| 6.11.5  | Status, Control and Configuration Register Map Parameter Table: 3 <sup>rd</sup> DWORD – Volatile registers address offset for die 2                |

| 6.11.6  | Status, Control and Configuration Register Map Parameter Table: 4 <sup>th</sup> DWORD – Non-Volatile registers address offset for die 2            |

| 6.11.7  | Status, Control and Configuration Register Map Parameter Table: 5 <sup>th</sup> DWORD – Volatile registers address offset for die 3                |

| 6.11.8  | Status, Control and Configuration Register Map Parameter Table: 6 <sup>th</sup> DWORD – Non-Volatile registers address offset for die 3            |

| 6.12    | Command Sequences to Change to Octal DDR (8D-8D-8D) mode                                                                                           |

| 6.12.1  | Command Sequences to Change to Octal DDR (8D-8D-8D) mode, Parameter Header: 1st DWORD121                                                           |

| 6.12.2  | Command Sequences to Change to Octal DDR (8D-8D) mode, Parameter Header: 2 <sup>nd</sup> DWORD121                                                  |

| 6.12.3  | Command Sequences to Change to Octal DDR (8D-8D) mode, Parameter Table: 1 <sup>st</sup> DWORD - First<br>Command Sequence                          |

| 6.12.4  | Command Sequences to Change to Octal DDR (8D-8D) mode, Parameter Table: 2 <sup>nd</sup> DWORD - First<br>Command Sequence (continued)              |

| 6.12.5  | Command Sequences to Change to Octal DDR (8D-8D-8D) mode, Parameter Table: 3 <sup>rd</sup> DWORD - 2 <sup>nd</sup><br>Command Sequence             |

| 6.12.6  | Command Sequences to Change to Octal DDR (8D-8D-8D) mode, Parameter Table: 4 <sup>th</sup> DWORD - 2 <sup>nd</sup><br>Command Sequence (continued) |

| 6.12.7  | Command Sequences to Change to Octal DDR (8D-8D-8D) mode, Parameter Table: 5 <sup>th</sup> DWORD - 3 <sup>rd</sup><br>Command Sequence             |

| 6.12.8  | Command Sequences to Change to Octal DDR (8D-8D-8D) mode, Parameter Table: 6 <sup>th</sup> DWORD - 3 <sup>rd</sup><br>Command Sequence (continued) |

| 6.12.9  | Command Sequences to Change to Octal DDR (8D-8D-8D) mode, Parameter Table: 7 <sup>th</sup> DWORD - 4 <sup>th</sup><br>Command Sequence             |

| 6.12.10 | Command Sequences to Change to Octal DDR (8D-8D-8D) mode, Parameter Table: 8 <sup>th</sup> DWORD - 4 <sup>th</sup><br>Command Sequence (continued) |

| 6.13    | x4 Quad IO with DS Parameter Header and Table                                                                                                      |

| 6.13.1  | x4 Quad IO with DS Parameter Header: 1st DWORD                                                                                                     |

| 6.13.2  | x4 Quad IO with DS Parameter Header: 2nd DWORD                                                                                                     |

| 6.13.3  | x4 Quad IO with DS Parameter Table: 1st DWORD - Command Codes used in 4S-4D-4D protocol mode                                                       |

| 6.13.4  | x4 Quad IO with DS Parameter Table: 2nd DWORD - Command Codes used in 4S-4D-4D protocol mode                                |

|---------|-----------------------------------------------------------------------------------------------------------------------------|

| 6.13.5  | x4 Quad IO with DS Parameter Table: 3rd DWORD - Memory Commands Supported in 4S-4D-4D protocol mode                         |

| 6.13.6  | x4 Quad IO with DS Parameter Table: 4th DWORD - Dummy cycles used for various frequencies126                                |

| 6.13.7  | x4 Quad IO with DS Parameter Table: 5th DWORD - Dummy cycles used for various frequencies127                                |

| 6.14    | Command Sequences to Change to Quad DDR (4S-4D-4D) mode                                                                     |

| 6.14.1  | Command Sequences to Change to Quad DDR (4S-4D-4D) mode, Parameter Header: 1st DWORD129                                     |

| 6.14.2  | Command Sequences to Change to Quad DDR (4S-4D-4D) mode, Parameter Header: 2nd DWORD129                                     |

| 6.14.3  | Command Sequences to Change to Quad DDR (4S-4D-4D) mode, Parameter Table: 1st DWORD - First<br>Command Sequence             |

| 6.14.4  | Command Sequences to Change to Quad DDR (4S-4D-4D) mode, Parameter Table: 2nd DWORD - First<br>Command Sequence (continued) |

| 6.14.5  | Command Sequences to Change to Quad DDR (4S-4D-4D) mode, Parameter Table: 3rd DWORD - 2nd<br>Command Sequence               |

| 6.14.6  | Command Sequences to Change to Quad DDR (4S-4D-4D) mode, Parameter Table: 4th DWORD - 2nd<br>Command Sequence (continued)   |

| 6.14.7  | Command Sequences to Change to Quad DDR (4S-4D-4D) mode, Parameter Table: 5th DWORD - 3rd<br>Command Sequence               |

| 6.14.8  | Command Sequences to Change to Quad DDR (4S-4D-4D) mode, Parameter Table: 6th DWORD - 3rd<br>Command Sequence (continued)   |

| 6.14.9  | Command Sequences to Change to Quad DDR (4S-4D-4D) mode, Parameter Table: 7th DWORD - 4th<br>Command Sequence               |

| 6.14.10 | Command Sequences to Change to Quad DDR (4S-4D-4D) mode, Parameter Table: 8th DWORD - 4th<br>Command Sequence (continued)   |

| 7       | Rules for Header and Table Additions and Modifications                                                                      |

| 8       | Legacy Compatibility                                                                                                        |

| Annex A | A (Informative) Procedure For Requesting Function Specific ID                                                               |

| Annex I | 3 (informative) Revision History                                                                                            |

| B.1     | Differences between JESD216D and JESD216C                                                                                   |

| B.2     | Differences between JESD216C and JESD216B                                                                                   |

| B.3     | Differences between JESD216B and JESD216A                                                                                   |

| B.4     | Differences between JESD216A and JESD216                                                                                    |

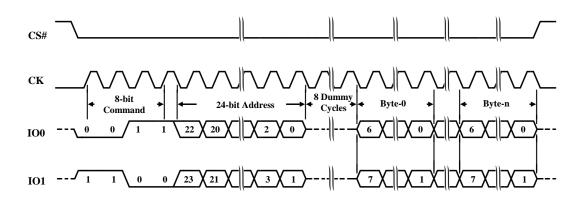

| Figure 1 — Read SFDP (1-1-1) Mode Timing Diagram                                                                           | 5  |

|----------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2 — Read SFDP (2-2-2) Mode Timing Diagram                                                                           | 6  |

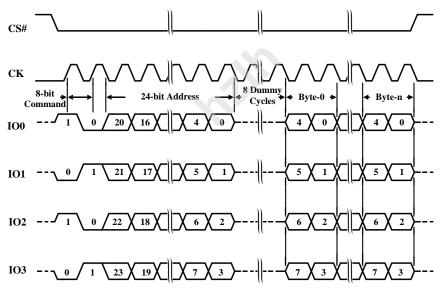

| Figure 3 — Read SFDP (4S-4S-4S) Mode Timing Diagram                                                                        | 6  |

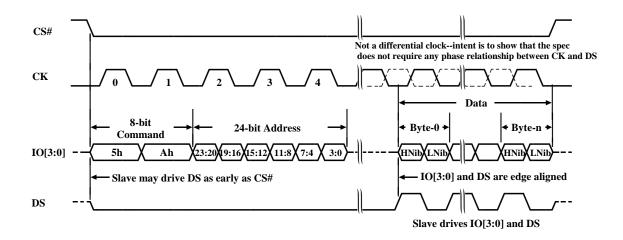

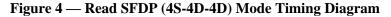

| Figure 4 — Read SFDP (4S-4D-4D) Mode Timing Diagram                                                                        | 7  |

| Figure 5 — Read SFDP (8D-8D-8D) Mode Timing Diagram                                                                        | 7  |

| Figure 6 — Fetch SFDP (1-1-1) Mode Timing Diagram                                                                          | 8  |

| Figure 7 — Fetch SFDP (2-2-2) Mode Timing Diagram                                                                          | 8  |

| Figure 8 — Fetch SFDP (4S-4S-4S and 4S-4D-4D) Mode Timing Diagram                                                          | 9  |

| Figure 9 — Fetch SFDP (8D-8D-8D) Mode Timing Diagram                                                                       | 9  |

| Figure 10 — Overall Header Structure                                                                                       | 11 |

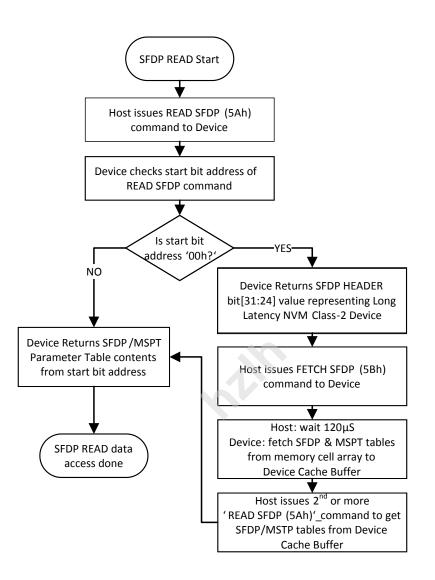

| Figure 11 — xSPI NAND Class-1 Device Read SFDP Flow                                                                        |    |

| Figure 12 — xSPI NAND Class-2 Device Read SFDP Flow                                                                        | 18 |

| Figure 13 — Example SFDP Header with single Basic Parameter Table                                                          | 22 |

| Figure 14 — Example SFDP Header with single Basic Parameter Table Word based (xSPI Profile 2.0)                            | 23 |

| Figure 15 — Example SFDP Header with two Basic parameter Tables                                                            | 23 |

| Figure 16 — Example SFDP Header with two basic Parameter Tables and one optional (4-Byte Address) Function Specific Tables |    |

| Figure 17 — Example SFDP Header with two basic Parameter Tables and two optional (4-Byte Address and                       | 23 |

| Status, Control and Configuration Register Map) Function Specific Tables                                                   | 24 |

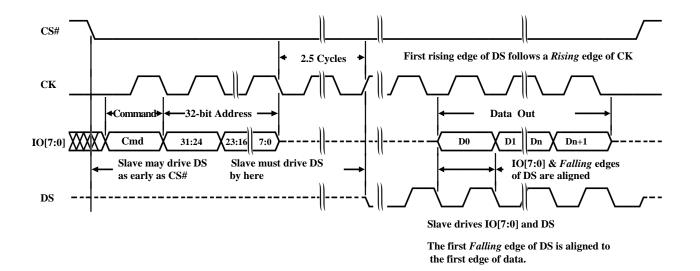

| Figure 18 — Data Strobe Waveforms in STR Mode – Option 11b                                                                 |    |

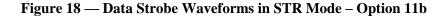

| Figure 19 — Data Strobe Waveforms in STR Mode - Option 10b                                                                 |    |

|                                                                                                                            |    |

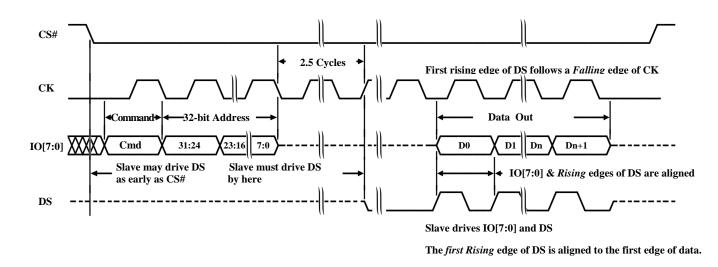

| Figure 20 — Data Strobe Waveforms in STR Mode - Option 01b                                                                 |    |

#### Foreword

This standard was prepared by the JEDEC SFDP Task Group authorized by the JC-42.4 Committee Chairman.

The intended audience is serial flash vendors and engineers writing device drivers for SFDP compliant serial flash devices.

The participating SFDP TG members included volunteers from Adesto, Cypress, Giga Device, Intel, ISSI, Macronix, Micron, Microchip, NXP, Sanyo, and Winbond.

#### Introduction

The Serial Flash Discoverable Parameter (SFDP) standard provides a consistent method of describing the functional and feature capabilities of serial flash devices in a standard set of internal parameter tables. These parameter tables can be interrogated by host system software to enable adjustments needed to accommodate divergent features from multiple vendors.

The SFDP standard defines a common parameter table describing important device characteristics and serial access methods used to read the parameter table data. Optional Special Function parameter tables for erase sector address map and 4-byte address instructions are included. New in the JESD216D revision are optional Special Function parameter tables for the JEDEC x4 (Quad) eXtended Serial Peripheral Interface (x4 xSPI). Additional parameter headers and tables can be specified by future revisions of this standard or by flash vendors and are optional.

# SERIAL FLASH DISCOVERABLE PARAMETERS (SFDP) STANDARD

(From JEDEC Board Ballot JCB-18-49, formulated under the cognizance of the JC-42.4 Committee on Nonvolatile Memory.)

| 1 | Scope |  |  |  |

|---|-------|--|--|--|

|---|-------|--|--|--|

The SFDP standard defines the structure of the SFDP database within the memory device and methods used to read its data.

The JEDEC-defined header with Parameter ID FF00h and the related Basic Parameter Table is mandatory. This header and table provide basic information for a Serial Peripheral Interface (SPI) protocol memory. Additional headers and tables are optional.

The read command protocol using various I/O modes and standard clock rate are specified. The device electrical parameters are not specified.

#### 2 Normative reference

The following normative documents contain provisions that, through reference in this text, constitute provisions of this standard. For dated references, subsequent amendments to, or revisions of, any of these publications do not apply. However, parties to agreements based on this standard are encouraged to investigate the possibility of applying the most recent editions of the normative documents listed. For undated references, the latest edition of the normative document referred to applies.

- 1. JEP106, Standard Manufacturers Identification Code (see <u>www.jedec.org</u> for latest revision)

- 2. NIST SP800-147, *BIOS Protection Guidelines* (<u>http://nvlpubs.nist.gov/nistpubs/Legacy/SP/nistspecialpublication800-147.pdf</u>)

- 3. JEDEC Standard JESD251, *eXpanded Serial Peripheral Interface (xSPI) for Non Volatile Memory Devices* as approved by JC42.4 committee in the June 2017 meeting.

JEDEC Standard JESDxxx, SPI Protocol Reset (Serial Peripheral Interface - Flash Hardware Reset Method, Not Requiring a Dedicated Reset Signal Input, **This document in development.**

4. JEDEC Standard JESD230C, NAND Flash Interface Interoperability

### **3** Terms and definitions

For the purposes of this standard, the following terms and definitions apply.

**00b:** The 'b' suffix indicates the '00' digits are a binary representation of the number.

**00h:** The 'h' suffix indicates the '00' digits are a hexadecimal representation of the number.

**address**: The three or four byte value following some instructions that is used to select a location within an address space of the flash memory.

**basic parameter table:** The table pointed to by Parameter ID FF00h. Contains general information about the flash device's capabilities.

block: A group of contiguous sectors.

**command:** The combination of the instruction, address, optional mode bits, wait states, and data cycles used to initiate functions or transfer information between the controller and the serial flash.

controller: The serial bus master

**Double Transfer Rate (DTR)**: Instruction, address, and/or data may be input or output on both the rising and falling edges of the clock. Note: The term "Double Data Rate" (DDR) may also be encountered in some documentation.

Data Strobe (DS): Slave to master strobe signal used to capture data sent by the slave.

dummy cycles: Clock cycles during which no data is transferred to or from a memory.

**DWORD:** Four consecutive 8-bit bytes used as the basic 32-bit building block for headers and parameter tables.

**instruction:** The one byte code used to initiate a function in the serial flash or identify the type of information transfer between the controller and the serial flash.

**mode bits:** Optional control bits that follow the address bits. These bits are driven by the controller if they are specified.

**wait states:** Required clock cycles between the address bits or optional mode bits and the start of data when reading from the flash device. Some device data sheets describe these as dummy cycles because no information is transferred between the controller and memory during these cycles. Neither controller nor memory are required to drive the data lines during these cycles.

**read latency:** On flash read instructions, the total number of clocks between end of address and the start of data. The sum of clocks for mode bits and clocks for wait states equals the Read Latency.

**sector:** The minimum granularity - size and alignment - of an area that can be erased in the data array of a flash memory device. Different areas within the address range of the data array may have a different minimum erase granularity (sector size).

### **3** Terms and difinitions (cont'd)

(x-y-z): Command mode nomenclature used in JESD216A and JESD216B to indicate the number of active pins used for the instruction (x), address (y), and data (z). For new entries in the current standard, this is replaced by the (An-Bn-Cn) nomenclature described below. The (x-y-z) nomenclature is equivalent to (AS-BS-CS) unless otherwise noted. (4-4-4) is therefore equivalent to (4S-4S-4S).

(An-Bn-Cn): Command mode nomenclature used to indicate the number of active pins used for the instruction (A), address (B), and data (C), and the data rate used for each. Data rates(n) can be single (S) and dual (D). At the present time, the only valid Read SFDP command modes are: (1S-1S-1S), (2S-2S-2S), (4S-4S-4S), (4S-4D-4D), and (8D-8D-8D). (4S-4D-4D), and (8D-8D-8D) modes also use a Data Strobe (DS) as part of the communication protocol.

#### 4 Read SFDP Command Protocol

#### 4.1 Instruction

The Read SFDP instruction code is 5Ah.

• The very first SFDP instruction a Device receives from a Host is the READ SFDP (5Ah) instruction during POR discovery phase.

The Fetch SFDP instruction code is 5Bh.

- This instruction is added to support Long Latency NVM Devices. This instruction tells a Device to load all parameter tables, defined in SFDP Header Structure, from device Memory Cell Array to Device Cache Buffer. NAND Flash device is the first Long Latency NVM device supported by SFDP. Host shall wait for 120 µs tR (Read Latency) then Host can re-issue Read SFDP (5Ah) instruction to access SFDP parameter table and Long Latency NVM device MSPT (Media Specific Parameter Table) table.

- Fetch SFDP (5Bh) instruction shall follow the same mode established between a Host and a Device during POR Read SFDP (5Ah) instruction phase.

NOTE Fetch SFDP instruction is only applicable for POR device discovery process for now. If needed, additional details of normal connected operation description would be available after JEDEC SPI NAND document is available.

#### 4.2 Address

Indicates the starting byte address in the SFDP area and is always expressed as a three byte field for (1S-1S-1S), (2S-2S-2S), (4S-4S-4S), and (4S-4D-4D) modes. For the (8D-8D-8D) mode, 3 or 4 byte addressing may be used.

• Fetch SFDP (5Bh) instruction does not have or require an address field.

# 4.3 Wait States

Following the address, eight clocks are required before valid data is clocked out for (1S-1S-1S), (2S-2S-2S), (4S-4S-4S), and (4S-4D-4D) modes. For the (8D-8D-8D) mode, a variable number of wait states (dummy cycles) may be used.

• Not applicable for Fetch SFDP (5Bh) instruction since it does not have an address field and does not output data.

## 4.4 Clock Rate

SFDP compliant devices must support 50 MHz operation for the Read SFDP command (instruction 5Ah). Devices may support a wider frequency range, but a controller can always run SFDP cycles at 50 MHz or less and get valid results.

• Fetch SFDP (5Bh) instruction shall follow the same mode established between a Host and a Device during Read SFDP (5Ah) instruction phase.

#### 4.5 Command Modes

The Read SFDP command can be used with device supported modes of (1-1-1), (2-2-2), (4-4-4), or (4S-4D-4D), but the instruction (5Ah), address (24 bits), eight wait states, and 50 MHz requirements remain the same. For the (8D-8D-8D) mode, the instruction (5Ah) and 50 MHz requirements remain the same, while 24 or 32 address bits, and a variable number of wait states (dummy cycles) may be used. Support for SFDP does not imply or require that the slave device supports 2-2-2, 4-4-4 or 8-8-8 mode. If the controller knows a priori the mode in which the flash device is configured, then it can issue the Read SFDP command in that mode. If the controller does not know, then a suggested algorithm is to try to read the SFDP signature (see 6.1) in 4-4-4 mode, if that fails try 2-2-2 mode, and if that fails try 1-1-1 mode. For Octal devices, these typically support SFDP read operation in both 1S-1S-1S mode and 8D-8D mode. If the host controller does not know exactly which protocol mode is used for SFDP in 8D-8D mode, this information can be found by reading SFDP in 1S-1S-1S mode first. (To read an unknown device directly in 8D-8D-8D mode, the host controller may read from address 0, and count the number of dummy clocks required before the SFDP signature is received.)

• Fetch SFDP (5Bh) instruction shall follow the same mode established between a Host and a Device during Read SFDP (5Ah) instruction phase.

#### 4.5 Command Modes (cont'd)

#### **Timing Diagram Signal Definitions:**

- CS# = Select, low active. Memory device selection signal also often referred to as Chip Select or Chip Enable

- CK = Clock. Serial clock to the memory also often referred to as SCLK.

- IO0 = Data input or output zero. The least significant memory data input or output also often referred to as DQ0 or Serial Input (SI) when not used for two, four or eight bit data I/O.

- IO1 = Data input or output one. The next most significant memory data input or output above IO0, also often referred to as DQ1 or Serial Output (SO) when not used for two, four or eight bit data I/O.

- IO2 = Data input or output two. The next most significant memory data input or output above IO1, also often referred to as DQ2 or Write Protect, low active (WP#) when not used for four or eight bit data I/O.

- IO3 = Data input or output three. The most significant memory data input or output, also often referred to as DQ3 or Hold, low active (HOLD#) when not used for four or eight bit data I/O.

- IO4-7 = Data input or output four to seven. Used for eight bit data I/O (8D-8D-8D). Also often referred to as DQ4-7.

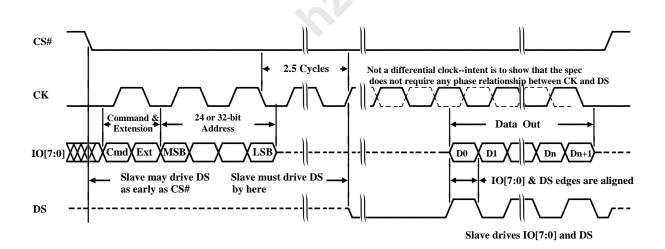

- DS = Data Strobe. Used for (4S-4D-4D) and (8D-8D-8D). The Data Strobe (DS) signal provides a timing reference for information transfer on the IO signals from the slave to the master. DS is an output signal from the xSPI slave device that is aligned with the edges of output data and is used by the host interface to optimize high frequency read data capture. DS may optionally be used as a signal from the slave to the master, to indicate the duration of initial access latency or, as a signal from the master to the slave, to indicate write data masking.

# 4.5.1 Read SFDP (1-1-1) Mode

Figure 1 — Read SFDP (1-1-1) Mode Timing Diagram

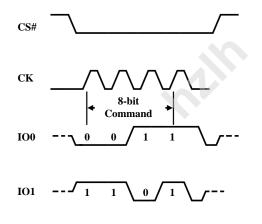

#### 4.5.2 Read SFDP (2-2-2) Mode

Figure 2 — Read SFDP (2-2-2) Mode Timing Diagram

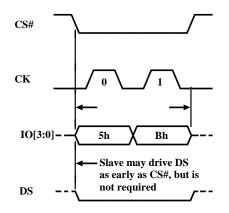

#### 4.5.3 Read SFDP (4S-4S-4S) Mode

Figure 3 — Read SFDP (4S-4S-4S) Mode Timing Diagram

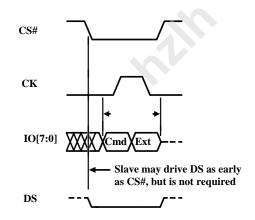

#### 4.5.4 Read SFDP (4S-4D-4D) Mode

NOTE DS is optional in this mode.

#### 4.5.5 Read SFDP (8D-8D-8D) Mode

See 6.4.21 for details about the addressing options in this mode.

Figure 5 — Read SFDP (8D-8D-8D) Mode Timing Diagram

JEDEC Standard No. 216D Page 8

#### 4.5.6 Fetch SFDP (1-1-1) Mode

Figure 6 — Fetch SFDP (1-1-1) Mode Timing Diagram

# 4.5.7 Fetch SFDP (2-2-2) Mode

Figure 7 — Fetch SFDP (2-2-2) Mode Timing Diagram

#### 4.5.8 Fetch SFDP (4S-4S-4S and 4S-4D-4D) Mode

Figure 8 — Fetch SFDP (4S-4S-4S and 4S-4D-4D) Mode Timing Diagram

#### 4.5.9 Fetch SFDP (8D-8D-8D) Mode

Figure 9 — Fetch SFDP (8D-8D-8D) Mode Timing Diagram

#### 5 Read SFDP Behavior

#### 5.1 Security

The SFDP and flash memory address ranges must never overlap. This ensures that address range checking the controller may perform to prevent access to security keys or other sensitive information stored in flash cannot be bypassed. Also, for PC BIOS applications non-overlap is required to comply with NIST SP800-147.

Addresses beyond the end of the SFDP tables must not alias into the flash memory. Regardless of the implementation, writes to SFDP tables must be permanently disabled before the memory device is released to a customer by the memory vendor factory.

#### 5.2 Reset and Hold Functions

Reset and Hold functionality will be available during the Read SFDP command if the memory device command mode supports these features. Note that these functions may not be available in all modes, as the pins used for Reset or Hold may be reused for I/O pins in Quad and Octal modes. The JEDEC SPI Protocol Reset is an alternative Reset function that may be used in any mode for devices which support it. See the JEDEC SPI Protocol Reset spec for details.

#### 5.3 Read Wrap

Not supported with the Read SFDP command--even when a memory device defaults to Read Wraparound mode for other read commands. Only continuous (sequential) read is supported with the Read SFDP command.

#### 5.4 SFDP Address Boundary Wrap

Device behavior when the Read SFDP command crosses the SFDP structure boundary is not defined except for the security restriction specified in 5.1. There is no requirement for the address counter to wrap back to the beginning of the structure and the data read after that point is not specified.

#### 5.5 Reserved SFDP Locations

The content of reserved SFDP locations (memory within the SFDP address space that has not yet been defined or used) is not specified, but recommended to be all FFh.

#### 6 SFDP Database

#### 6.1 SFDP Header Structure

The format of the SFDP header is shown in Figure 10 — Overall Header Structure.

|                           | [31:24]             | [23:16]            | [15:8]           | [7:0]           | Hex byte<br>location |

|---------------------------|---------------------|--------------------|------------------|-----------------|----------------------|

| SFDP Header               | Serial Flash Discov | verable Parameters | (SFDP) Signat    | ure = 50444653h | [3h:0h]              |

|                           | Byte 3 = "P"        | Byte $2 = "D"$     | Byte $1 = "F"$   | Byte $0 = "S"$  |                      |

|                           | SFDP Access         | Number of          | SFDP Major       | SFDP Minor      | [7h:4h]              |

|                           | Protocol            | Parameter          | Revision         | Revision        |                      |

|                           |                     | Headers (NPH)      |                  |                 |                      |

| 1 <sup>st</sup> Parameter | Parameter Length    | Parameter          | Parameter        | Parameter ID    | [Bh:8h]              |

| Header                    | (in double words)   | Major Revision     | Minor            | LSB             |                      |

|                           |                     |                    | Revision         | JEDEC ID (00h)  |                      |

|                           | Parameter ID        | Parameter 7        | Fable Pointer (b | yte address)    | [Fh:Ch]              |

|                           | MSB                 |                    |                  |                 |                      |

|                           | JEDEC ID (FFh)      |                    |                  |                 |                      |

| 2 <sup>nd</sup> Parameter | Parameter Length    | Parameter          | Parameter        | Parameter ID    | [13h:10h]            |

| Header                    | (in double words)   | Major Revision     | Minor            | LSB             |                      |

| (optional)                |                     |                    | Revision         |                 |                      |

|                           | Parameter ID        | Parameter 7        | Fable Pointer (b | oyte address)   | [17h:14h]            |

|                           | MSB                 |                    |                  |                 |                      |

|                           |                     |                    |                  |                 |                      |

| Nth                       | Parameter Length    | Parameter          | Parameter        | Parameter ID    |                      |

| Parameter                 | (in double words)   | Major Revision     | Minor            | LSB             |                      |

| Header                    |                     |                    | Revision         |                 |                      |

| (optional)                | Parameter ID<br>MSB | Parameter          | Fable Pointer (b | yte address)    |                      |

Figure 10 — Overall Header Structure

## 6.2 SFDP Header

The SFDP Header is located at address 000000h of the SFDP data structure. It identifies the SFDP Signature, the number of parameter headers, and the SFDP revision numbers.

Both the SFDP header and the individual parameter table headers include Major and Minor revision numbers.

Major revisions require code (BIOS/firmware) or hardware change to get previously defined discoverable parameters. For example, changes that reorganize previously defined fields.

Minor revisions are changes that define previously reserved fields, add fields to the end, or that clarify definitions of existing fields.

JESD216B maintains backwards compatibility with JESD216A, defines previously reserved bits in the15<sup>th</sup> DWORD of the Basic Flash Parameter Table and adds optional Function Specific table definitions.

JESD216C maintains backwards compatibility with JESD216B, defines previously reserved bits in the 2<sup>nd</sup> DWORD of the SFDP Header and adds optional Function Specific table definitions.

JESD216D maintains backwards compatibility with JESD216C.

The revision numbers of vendor-defined and Function Specific tables follow the same guidelines as the Basic Parameter Table.

#### Major vs. Minor Revisions

Major revisions indicate that the table structure has changed and may not be backwards compatible with software written for an earlier revision of SFDP.

Increments of minor revisions indicate that fields or DWORDS have been added but the definition of existing fields is unchanged. Software should accept any minor revision number and read only the number of parameter table fields that the software requires. Users should accept any minor revision greater than or equal to the current revision. All fields defined in the current tables will be unchanged in subsequent minor revisions. Undefined or reserved fields may be updated.

#### 6.2.1 SFDP Header: 1<sup>st</sup> DWORD

| Bits | Description                                                                   |

|------|-------------------------------------------------------------------------------|

| 31:0 | <b>SFDP Signature</b><br>Allows a user to know that the information is valid. |

|      | Signature[31:0]: 50444653h                                                    |

| 6.2.2 | SFDP Header: 2 <sup>nd</sup> DWORD |

|-------|------------------------------------|

|-------|------------------------------------|

| Bits  | Description                                                                                                                                                                                                                                                                                                                                       |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | SFDP Access Protocol                                                                                                                                                                                                                                                                                                                              |

| 51.24 | See 0                                                                                                                                                                                                                                                                                                                                             |

|       | Number of Parameter Headers (NPH)                                                                                                                                                                                                                                                                                                                 |

|       | Specifies the number of parameter headers in the SFDP data structure.                                                                                                                                                                                                                                                                             |

| 23:16 | This number is 0-based. Therefore, 0 indicates 1 parameter header.                                                                                                                                                                                                                                                                                |

|       | The value of this field is not defined by this standard. It is dependent on the number of tables                                                                                                                                                                                                                                                  |

|       | a vendor implements. The value FFh is reserved for future extensions of this standard.                                                                                                                                                                                                                                                            |

| 15:8  | <ul> <li>SFDP Major Revision Number</li> <li>This 8-bit field indicates the major revision number of this standard. The value in this field is 1 for devices which implement the JESD216D revision (unchanged from JESD216C revision).</li> <li>NOTE The value of this field may only be changed by an update to the JESD216 standard.</li> </ul> |

| 7:0   | <b>SFDP Minor Revision Number</b><br>This 8-bit field indicates the minor revision number of this standard. The value in this field is 8 for devices which implement the JESD216D revision.<br>NOTE The value of this field may only be changed by an update to the JESD216 standard.                                                             |

|       |                                                                                                                                                                                                                                                                                                                                                   |

# 6.2.3 Definition of SFDP Access Protocol Field

The purpose of the Access Protocol Field is to provide the host controller necessary information about how to read the SFDP command. In early versions of this spec (up to and including JESD216B) this field was FFh. The value FFh still indicates that the SFDP command structure is backwards compatible with the description given in JESD216B. The device will in this case respond to one or more of the SFDP command options as described in JESD216B. Any other value indicates that the SFDP command will behave differently in one or more aspects.

(8D-8D-8D) devices still use FFh as the parameter value if they boot up in one of the modes that are compatible with the JESD216B revision. (Typically this would be (1S-1S-1S) mode.)

For devices where the boot mode may be changed by the user by setting fuses or similar, the device has to update the value returned in the SFDP Access Protocol Field according to the fuse settings.

| SFDP Command    |                                                                                                        |                                                                                                                                                                            |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameter Value |                                                                                                        |                                                                                                                                                                            |  |  |  |

| Decimal         | Hex                                                                                                    |                                                                                                                                                                            |  |  |  |

| 0-239           | 00h-EFh                                                                                                | Reserved for future use                                                                                                                                                    |  |  |  |

| 240             | F0h                                                                                                    | xSPI NAND class-1 device – parameter data is available in device cache buffer.                                                                                             |  |  |  |

|                 |                                                                                                        | xSPI Octal, (8D, 8D, 8D) operation, 4-byte addressing for SFDP command, 8 wait states.                                                                                     |  |  |  |

|                 |                                                                                                        | NAND Flash devices use JESD230C Parameter Page as MSPT.                                                                                                                    |  |  |  |

|                 | Follow Long latency NVM Class-1 device SFDP access behavior for reading SFD MSPT data (see Figure 11): |                                                                                                                                                                            |  |  |  |

|                 |                                                                                                        | SFDP Parameter Table & NVM Media Specific Parameter Table are available in Device's Cache Buffer before Device is ready to process Host commands during POR process,       |  |  |  |

|                 |                                                                                                        | 1. After POR, Host always first issue READ SFDP (5Ah) with start address '00h' for device discovery                                                                        |  |  |  |

|                 |                                                                                                        | • Device returns the SFDP Header with the appropriate parameter value code representing NVM Class-1 Device after received READ SFDP (5Ah) command with start address '00h' |  |  |  |

|                 |                                                                                                        | 2. Host issues 2 <sup>nd</sup> (and more if needed) READ SFDP (5Ah) command(s) with a non-zero start address to access SFDP and MSPT table contents                        |  |  |  |

|                 |                                                                                                        | Device returns the SFDP/MSPT table data beginning from the start address specified in READ SFDP (5Ah) command.                                                             |  |  |  |

| SFDP Cor<br>Parameter |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Decimal               | Hex |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 241                   | F1h | xSPI NAND class-2 device – parameter data is not available in device cache buffer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                       |     | xSPI Octal, (8D, 8D, 8D) operation, 4-byte addressing for SFDP command, 8 wait states.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       |     | NAND Flash devices use JESD230C Parameter Page as MSPT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       |     | <ul> <li>Follow Long latency NVM Class-2 device SFDP access behavior for reading SFDP &amp; MSPT data (see Error! Reference source not found.):</li> <li>Parameter Tables are not available in the device's Cache Buffer before Device is ready to process Host commands during POR process,</li> <li>1. After POR, Host always first issue READ SFDP (5Ah) with start address '00h' for device discovery</li> <li>Device returns SFDP Header with the appropriate parameter value code representing NVM Class-2 Device after received READ SFDP (5Ah) command with '00h' start address</li> <li>2. Host issue FETCH SFDP (5Bh) command to Device</li> <li>3. Host: wait 120µs; Device: fetches SFDP &amp; MSPT tables from memory cell array to Device's Cache Buffer</li> <li>4. Host issues 2<sup>nd</sup> (and more if needed) READ SFDP (5Ah) command(s) with a non-zero start address to access SFDP and MSPT table contents</li> <li>Device returns the SFDP/MSPT Table data beginning from the start address specified in READ SFDP (5Ah) command</li> </ul> |

| 242                   | F2h | Reserved for xSPI NAND class-3 device, Combo device includes both NOR Flash & Class-1<br>Long Latency NVM.<br>-for octal interface to low Latency combo with SFDP table in the cache and can use a 5Ah<br>command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 243                   | F3h | Reserved for xSPI NAND class-3 device – combo device with both NOR Flash device and<br>Class-2 Long Latency NVM device<br>-for octal interface to low Latency combo with SFDP table is not in the cache and requires<br>a 5Bh command before the 5Ah command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 244                   | F4h | <ul> <li>SPI NAND class-1 device – parameter data is available in device cache buffer Legacy option: Behavior consistent with JESD216B revision.</li> <li>(1S-1S-1S), (2S-2S-2S) or (4S-4S-4S) operation, 3-byte addressing for SFDP command, 8 wait states.</li> <li>NAND Flash devices use JESD230C Parameter Page as MSPT</li> <li>Follow Long latency NVM Class-1 device SFDP access behavior for reading SFDP &amp; MSPT data (see Figure 11)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SFDP Command<br>Parameter Value |         |                                                                                                                                                |

|---------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Decimal                         | Hex     |                                                                                                                                                |

| 245 F5h                         |         | SPI NAND class-2 device – parameter data is not available in device cache buffer<br>Legacy option: Behavior consistent with JESD216B revision. |

|                                 |         | (1S-1S-1S), (2S-2S-2S) or (4S-4S-4S) operation, 3-byte addressing for SFDP command, 8 wait states.                                             |

|                                 |         | NAND Flash devices use JESD230C Parameter Page as MSPT                                                                                         |

|                                 |         | Follow Long latency NVM Class-2 device SFDP access behavior for reading SFDP & MSPT data                                                       |

| 246                             | F6h     | Reserved for SPI NAND class-3 device, Combo device includes both NOR Flash & Class-1<br>Long Latency NVM.                                      |

| 247                             | F7h     | Reserved for SPI NAND class-3 device, Combo device includes both NOR Flash & SPI                                                               |

|                                 |         | Class-2 Long Latency NVM.                                                                                                                      |

| 248:249                         | F8h:F9h | Reserved for future use                                                                                                                        |

| 250                             | FAh     | xSPI NOR Profile 2 (8D, 8D, 8D) operation, 5-byte addressing, SFDP command                                                                     |

|                                 |         | (WREN1 & WREN2), Configurable wait states.                                                                                                     |

| 251                             | FBh     | Reserved for future use                                                                                                                        |

| 252                             | FCh     | xSPI NOR Profile 1 Octal, (8D, 8D, 8D) operation, 3-byte                                                                                       |

|                                 |         | addressing $+ 1/2$ Cycle for Octal DTR Alignment for SFDP command, 8 wait states.                                                              |

| 253                             | FDh     | xSPI NOR Profile 1 Octal, (8D, 8D, 8D) operation, 4-byte                                                                                       |

|                                 |         | addressing for SFDP command, 20 wait states.                                                                                                   |

| 254                             | FEh     | xSPI NOR Profile 1 Octal, (8D, 8D, 8D) operation, 4-byte                                                                                       |

|                                 |         | addressing for SFDP command, 8 wait states.                                                                                                    |

| 255                             | FFh     | Legacy option: Behavior consistent with JESD216B revision.                                                                                     |

|                                 |         | (1S-1S-1S), (2S-2S-2S) or (4S-4S-4S) operation, 3-byte addressing for SFDP                                                                     |

|                                 |         | command, 8 wait states.                                                                                                                        |

# SFDP READ Start Host issues READ SFDP (5Ah) command to Device ¥ Device check start bit address of **READ SFDP command** Is start bit YESaddress '00h?; **Device Returns SFDP** NO HEADER bit [31:24] value representing Long Latency NVM Class-1 Device ¥ Host issues 2<sup>nd</sup> or more Device Returns SFDP/MSPT 'READ SFDP (5Ah)'\_command to get Parameter Table contents SFDP/MSTP tables from Device from start bit address Cache Buffer SFDP READ data access done

#### 6.3 Parameter Headers

Each Parameter Header identifies the size, location, revision, ownership and function of their associated parameter tables. Parameter table ownership will be either JEDEC (via this standard) or an individual vendor (via vendor specific documentation).

Multiple parameter headers can be specified with each parameter header being 2 DWORDs (64-bits). The first parameter header is mandatory, is defined by this standard, and starts at byte offset 08h. If a vendor chooses to include multiple revisions of the Basic Parameter Table they may do so provided the table headers are in order starting with the oldest version. The total number of parameter headers is specified in the NPH field of the SFDP header, see 0. All subsequent parameter headers need to be contiguous and may be specified by JEDEC or by vendors using the same structure (shown in Figure 10). Minor revisions may overlap earlier revisions by starting at the same address as an earlier revision but have additional length for parameters added in the later revision. This allows the use of legacy parameters without the need to repeat them in each new minor revision.

| Bits  | Description                                                                                                                                                                                                              |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | Parameter Table Length<br>This field specifies how many DWORDs are in the Parameter table.                                                                                                                               |