# JEDEC STANDARD

Serial Flash Discoverable Parameters (SFDP)

JESD216A

**JULY 2013**

JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

#### **NOTICE**

JEDEC standards and publications contain material that has been prepared, reviewed, and approved through the JEDEC Board of Directors level and subsequently reviewed and approved by the JEDEC legal counsel.

JEDEC standards and publications are designed to serve the public interest through eliminating misunderstandings between manufacturers and purchasers, facilitating interchangeability and improvement of products, and assisting the purchaser in selecting and obtaining with minimum delay the proper product for use by those other than JEDEC members, whether the standard is to be used either domestically or internationally.

JEDEC standards and publications are adopted without regard to whether or not their adoption may involve patents or articles, materials, or processes. By such action JEDEC does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the JEDEC standards or publications.

The information included in JEDEC standards and publications represents a sound approach to product specification and application, principally from the solid state device manufacturer viewpoint. Within the JEDEC organization there are procedures whereby a JEDEC standard or publication may be further processed and ultimately become an ANSI standard.

No claims to be in conformance with this standard may be made unless all requirements stated in the standard are met.

Inquiries, comments, and suggestions relative to the content of this JEDEC standard or publication should be addressed to JEDEC at the address below, or refer to <a href="www.jedec.org">www.jedec.org</a> under Standards and Documents for alternative contact information.

Published by

©JEDEC Solid State Technology Association 2013

3103 North 10th Street

Suite 240 South

Arlington, VA 22201-2107

This document may be downloaded free of charge; however JEDEC retains the copyright on this material. By downloading this file the individual agrees not to charge for or resell the resulting material.

**PRICE: Contact JEDEC**

Printed in the U.S.A. All rights reserved

chenodii

# SERIAL FLASH DISCOVERABLE PARAMETERS (SFDP) STANDARD

## **Contents**

|            |                                                                  | Page   |

|------------|------------------------------------------------------------------|--------|

| Fore       | word                                                             | ii     |

| Intro      | duction                                                          | ii     |

| 1          | Scope                                                            | 1      |

| 2          | Normative references                                             | 1      |

| 3          | Terms and definitions                                            | 1      |

| 4          | Read SFDP Command Protocol                                       | 3      |

| 4.1        | Instruction                                                      | 3      |

| 4.2        | Address                                                          | 3      |

| 4.3        | Wait States                                                      | 3      |

| 4.4        | Clock Rate                                                       | 3      |

| 4.5        | Command Modes                                                    | 3      |

| 4.5.1      | Read SFDP (1-1-1) Mode                                           | 4      |

| 4.5.2      | Read SFDP (2-2-2) Mode                                           | 4      |

| 4.5.3      | Read SFDP (4-4-4) Mode                                           | 5<br>5 |

| 5          | Read SFDP Behavior                                               | 5      |

| <b>5.1</b> | Security                                                         | 5      |

| <b>5.2</b> | Reset and Hold Functions                                         | 5      |

| <b>5.3</b> | Read Wraps                                                       | 5      |

| <b>5.4</b> | SFDP Address Boundary Wrap                                       | 6      |

| 5.5        | Reserved SFDP Locations                                          | 6      |

| 6          | SFDP Database                                                    | 6      |

| 6.1        | SFDP Header Structure                                            | 6      |

| 6.2        | SFDP Header                                                      | 7      |

| 6.2.1      | SFDP Header: 1 <sup>st</sup> DWORD                               | 7      |

| 6.2.2      | SFDP Header: 2 <sup>nd</sup> DWORD                               | 7      |

| 6.3        | Parameter Headers                                                | 8      |

| 6.3.1      | Parameter Header: 1 <sup>st</sup> DWORD                          | 8      |

| 6.3.2      | Parameter Header: 2 <sup>nd</sup> DWORD                          | 8      |

| 6.3.3      | Example of an SFDP Header                                        | 10     |

| 6.4        | JEDEC Basic Flash Parameter Table                                | 10-28  |

| 7          | Rules for Header and Table Additions and Modifications           | 29     |

| 8          | Legacy Compatibility                                             | 29     |

| Anne       | ex A (informative) Example SFDP Discovery Code                   | 30     |

|            | ex B (informative) Procedure For Requesting Function Specific ID | 32     |

|            | ex C (informative) Revision History                              | 32     |

|            |                                                                  |        |

| Figu       | res                                                              |        |

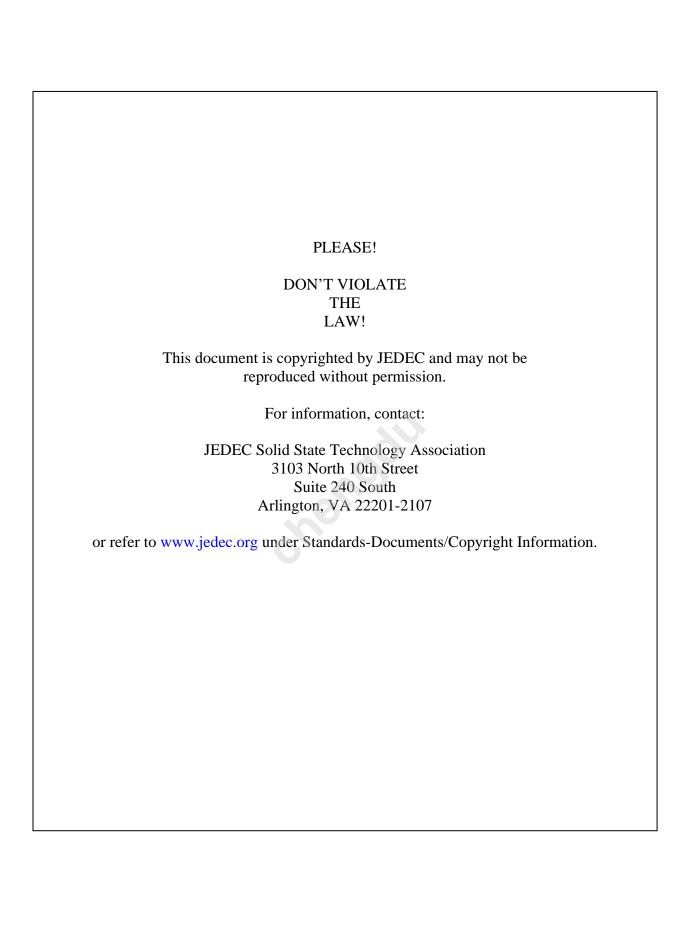

| 1          | Read SFDP (1-1-1) Mode Timing Diagram                            | 4      |

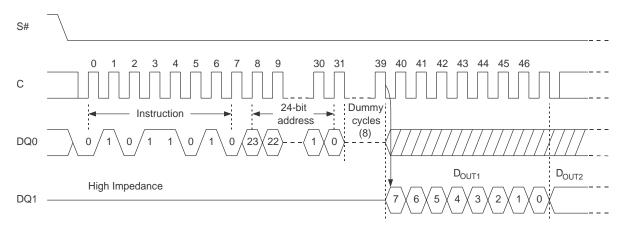

| 2          | Read SFDP (2-2-2) Mode Timing Diagram                            | 4      |

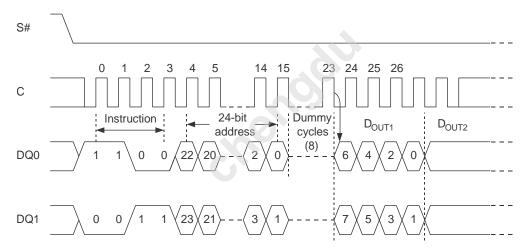

| 3          | Read SFDP (4-4-4) Mode Timing Diagram                            | 5      |

| 4          | Overall Header Structure                                         | 6      |

| 5          | Example of an SFDP Header                                        | 10     |

#### **Foreword**

This standard was prepared by the JEDEC SFDP Task Group authorized by the JC-42.4 Committee Chairman. It was derived from prior work done by Intel on their 'Serial Flash Discoverable Parameters Guidelines' document.

The intended audience is serial flash vendors and engineers writing device drivers for SFDP compliant serial flash devices.

The participating SFDP TG members were volunteers from AMD, ASPEED, Emulex, Intel, Macronix, Micron, Microchip, Sanyo, Spansion, and Winbond.

#### Introduction

The Serial Flash Discoverable Parameter (SFDP) standard provides a consistent method of describing the functional and feature capabilities of serial flash devices in a standard set of internal parameter tables. These parameter tables can be interrogated by host system software to enable adjustments needed to accommodate divergent features from multiple vendors.

The SFDP standard defines a common parameter table describing important device characteristics and serial access methods used to read the parameter table data. Additional parameter headers and tables can be specified by future revisions of this standard or by flash vendors and are optional.

## SERIAL FLASH DISCOVERABLE PARAMETERS (SFDP) STANDARD

(From JEDEC Board Ballot JCB-13-01, formulated under the cognizance of the JC-42.4 Committee on Nonvolatile Memory.)

#### 1 Scope

The SFDP standard defines the structure of the SFDP database within the memory device and methods used to read its data.

The JEDEC-defined header with Parameter ID FF00h and the related Basic Parameter Table is mandatory. This header and table provide basic information for a Serial Peripheral Interface (SPI) protocol memory. Additional headers and tables are optional.

The read command protocol using various I/O modes and standard clock rate are specified. The device electrical parameters are not specified.

#### 2 Normative reference

The following normative documents contain provisions that, through reference in this text, constitute provisions of this standard. For dated references, subsequent amendments to, or revisions of, any of these publications do not apply. However, parties to agreements based on this standard are encouraged to investigate the possibility of applying the most recent editions of the normative documents indicated below. For undated references, the latest edition of the normative document referred to applies.

- 1. JEP106, Standard Manufacturers Identification Code (contact jedec.org for the latest revision of this document)

- 2. NIST SP800-147, BIOS Protection Guidelines (http://csrc.nist.gov/publications/nistpubs/)

#### 3 Terms and definitions

For the purposes of this standard, the following terms and definitions apply:

00b: The 'b' suffix indicates the '00' digits are a binary representation of the number.

00h: The 'h' suffix indicates the '00' digits are a hexadecimal representation of the number.

0x00: The '0x' prefix indicates the '00' digits are a hexadecimal representation of the number. This form is used in the 'C' sample code in the Appendix.

Address: The three or four byte value following some instructions that is used to select a location within an address space of the flash memory.

## 3 Terms and definitions (cont'd)

Basic Parameter Table: The table pointed to by Parameter ID FF00h. Contains general information about the flash device's capabilities.

Command: The combination of the instruction, address, optional mode bits, wait states, and data cycles used to initiate functions or transfer information between the controller and the serial flash.

Controller: The serial bus master

Double Transfer Rate (DTR). Instruction, address, and/or data may be input or output on both the rising and falling edges of the clock.

Dummy Cycles: Clock cycles during which no data is transferred to or from a memory.

DWORD: Four consecutive 8-bit bytes used as the basic 32-bit building block for headers and parameter tables.

Instruction: The one byte code used to initiate a function in the serial flash or identify the type of information transfer between the controller and the serial flash.

Mode Bits: Optional control bits that follow the address bits. These bits are driven by the controller if they are specified.

Wait States: Required clock cycles between the address bits or optional mode bits and the start of data when reading from the flash device. Some device data sheets describe these as dummy cycles because no information is transferred between the controller and memory during these cycles. Neither controller nor memory are required to drive the data lines during these cycles.

Read Latency: On flash read instructions, the total number of clocks between end of address and the start of data. The sum of clocks for mode bits and clocks for wait states equals the Read Latency.

(x-y-z): Command mode nomenclature used to indicate the number of active pins used for the instruction (x), address (y), and data (z). At the present time, the only valid Read SFDP command modes are: (1-1-1), (2-2-2), and (4-4-4)

#### 4 Read SFDP Command Protocol

#### 4.1 Instruction

The Read SFDP instruction code is 5Ah.

#### 4.2 Address

Indicates the starting read location in the SFDP area and is always expressed as a three byte (24-bit) address.

#### 4.3 Wait States

Following the address, eight clocks are required before valid data is clocked out.

#### 4.4 Clock Rate

SFDP compliant devices must support 50 MHz operation for the Read SFDP command (instruction 5Ah). Devices may support a wider frequency range, but a controller can always run SFDP cycles at 50 MHz or less and get valid results.

## 4.5 Command Modes

The Read SFDP command can be used with device supported modes of (1-1-1), (2-2-2), or (4-4-4), but the instruction (5Ah), address (24 bits), eight wait states, and 50 MHz requirements remain the same. Support for SFDP does not imply or require that the flash device support 2-2-2 or 4-4-4 mode. If the controller knows a priori the mode in which the flash device is configured, then it can issue the Read SFDP command in that mode. If the controller does not know, then a suggested algorithm is to try to read the SFDP signature (see 6.1) in 4-4-4 mode, if that fails try 2-2-2 mode, and if that fails try 1-1-1 mode.

Timing Diagram Signal Definitions:

- S# = Select, low active. Memory device selection signal also often referred to as Chip Select or Chip Enable

- C = Clock. Serial clock to the memory also often referred to as SCLK.

- DQ0 = Data input or output zero. The least significant memory data input or output also often referred to as IO0 or Serial Input (SI) when not used for two or four bit data I/O.

- DQ1 = Data input or output one. The next most significant memory data input or output above DQ0, also often referred to as IO1 or Serial Output (SO) when not used for two or four bit data I/O.

- DQ2 = Data input or output two. The next most significant memory data input or output above DQ1, also often referred to as IO2 or Write Protect, low active (WP#) when not used for four bit data I/O.

- DQ3 = Data input or output three. The most significant memory data input or output, also often referred to as IO3 or Hold, low active (HOLD#) when not used for four bit data I/O.

## **4.5.1** Read SFDP (1-1-1) Mode

Figure 1 — Read SFDP (1-1-1) Mode Timing Diagram

## 4.5.2 Read SFDP (2-2-2) Mode

Figure 2 — Read SFDP (2-2-2) Mode Timing Diagram

## 4.5.3 Read SFDP (4-4-4) Mode

Figure 3 — Read SFDP (4-4-4) Mode Timing Diagram

#### 5 Read SFDP Behavior

## 5.1 Security

The SFDP and flash memory address ranges must never overlap. This ensures that address range checking the controller may perform to prevent access to security keys or other sensitive information stored in flash cannot be bypassed. Also, for PC BIOS applications non-overlap is required to comply with NIST SP800-147.

Addresses beyond the end of the SFDP tables must not alias into the flash memory. Regardless of the implementation, writes to SFDP tables must be permanently disabled before the memory device is released to a customer by the memory vendor factory.

#### **5.2** Reset and Hold Functions

Reset and Hold functionality will be available during the Read SFDP command if the memory device command mode supports these features.

## 5.3 Read Wrap

Not supported with the Read SFDP command--even when a memory device defaults to Read Wraparound mode for other read commands. Only continuous (sequential) read is supported with the Read SFDP command.

## 5.4 SFDP Address Boundary Wrap

Device behavior when the Read SFDP command crosses the SFDP structure boundary is not defined except for the security restriction specified in 5.1. There is no requirement for the address counter to wrap back to the beginning of the structure and the data read after that point is not specified.

## **5.5** Reserved SFDP Locations

The content of reserved SFDP locations (memory within the SFDP address space that has not yet been defined or used) is not specified, but recommended to be all FFh.

#### **6** SFDP Database

## **6.1** SFDP Header Structure

The format of the SFDP header is shown in Figure 4.

|                           | [31:24]             | [23:16]                                | [15:8]                 | [7:0]                  | Hex byte location |

|---------------------------|---------------------|----------------------------------------|------------------------|------------------------|-------------------|

| SFDP Header               |                     | overable Parameters (SFDP) Signature = |                        | [3h:0h]                |                   |

|                           | 50444653h           | D-4- 2 "D"                             | Davida 1 "E"           | D4- 0 "G"              |                   |

|                           | Byte 3 = "P"        | Byte 2 = "D"                           | Byte 1 = "F"           | Byte 0 = "S"           | [7]4]             |

|                           | Unused (set to FFh) | Number of Parameter                    | SFDP Major<br>Revision | SFDP Minor<br>Revision | [7h:4h]           |

|                           | rrii)               | Headers                                | Revision               | Revision               |                   |

|                           |                     | (NPH)                                  |                        |                        |                   |

| 1 <sup>st</sup> Parameter | Parameter Length    | Parameter                              | Parameter              | Parameter ID           | [Bh:8h]           |

| Header                    | (in double words)   | Major                                  | Minor                  | LSB                    |                   |

|                           |                     | Revision                               | Revision               | JEDEC ID               |                   |

|                           |                     |                                        |                        | (00h)                  |                   |

|                           | Parameter ID        | Par                                    | ameter Table Poi       | nter                   | [Fh:Ch]           |

|                           | MSB                 |                                        |                        |                        |                   |

|                           | JEDEC ID (FFh)      |                                        |                        |                        |                   |

| 2 <sup>nd</sup> Parameter | Parameter Length    | Parameter                              | Parameter              | Parameter ID           | [13h:10h]         |

| Header                    | (in double words)   | Major                                  | Minor                  | LSB                    |                   |

| (optional)                |                     | Revision                               | Revision               |                        |                   |

|                           | Parameter ID        | Par                                    | ameter Table Poi       | nter                   | [17h:14h]         |

|                           | MSB                 |                                        |                        |                        |                   |

|                           |                     |                                        |                        |                        |                   |

| Nth Parameter             | Parameter Length    | Parameter                              | Parameter              | Parameter ID           |                   |

| Header                    | (in double words)   | Major                                  | Minor                  | LSB                    |                   |

| (optional)                |                     | Revision                               | Revision               |                        |                   |

|                           | Parameter ID        | Par                                    | ameter Table Poi       | nter                   |                   |

|                           | MSB                 |                                        |                        |                        |                   |

Figure 4 — Overall Header Structure

#### 6.2 SFDP Header

The SFDP Header is located at address 000000h of the SFDP data structure. It identifies the SFDP Signature, the number of parameter headers, and the SFDP revision numbers.

Both the SFDP header and the individual parameter table headers include Major and Minor revision numbers.

Major revisions require code (BIOS/firmware) or hardware change to get previously defined discoverable parameters. For example, changes that reorganize previously defined fields.

Minor revisions are changes that define previously reserved fields, add fields to the end, or that clarify definitions of existing fields.

Revision A of JESD216 maintains backwards compatibility by appending new fields to the end of the previous Basic Parameter Table.

The revision numbers of vendor-defined and Function Specific tables follow the same guidelines as the Basic Parameter Table.

## 6.2.1 SFDP Header: 1<sup>st</sup> DWORD

| Bits | Description                                                         |

|------|---------------------------------------------------------------------|

| 31:0 | SFDP Signature Allows a user to know that the information is valid. |

|      | Signature[31:0]: 50444653h                                          |

# 6.2.2 SFDP Header: 2<sup>nd</sup> DWORD

| Bits  | Description                                                                                       |

|-------|---------------------------------------------------------------------------------------------------|

| 31:24 | Unused                                                                                            |

| 31.24 | Contains FFh and can never be changed.                                                            |

|       | Number of Parameter Headers (NPH)                                                                 |

|       | Specifies the number of parameter headers in the SFDP data structure.                             |

| 23:16 | This number is 0-based. Therefore, 0 indicates 1 parameter header.                                |

|       | The value of this field is not defined by this standard. It is dependent on the number of tables  |

|       | a vendor implements.                                                                              |

|       | SFDP Major Revision Number                                                                        |

|       | This 8-bit field indicates the major revision number of this standard. The value in this field is |

| 15:8  | 1 for devices which implement the JESD216A revision.                                              |

|       | NOTE The value of this field may only be changed by an update to the JESD216 standard.            |

| 7:0   | SFDP Minor Revision Number                                                                        |

|       | This 8-bit field indicates the minor revision number of this standard. The value in this field is |

|       | 5 for devices which implement the JESD216A revision.                                              |

|       | NOTE The value of this field may only be changed by an update to the JESD216 standard.            |

#### **6.3** Parameter Headers

Each Parameter Header identifies the size, location, revision, ownership and function of their associated parameter tables. Parameter table ownership will be either JEDEC (via this standard) or an individual vendor (via vendor specific documentation).

Multiple parameter headers can be specified with each parameter header being 2 DWORDs (64-bits). The first parameter header is mandatory, is defined by this standard, and starts at byte offset 08h. If a vendor chooses to include multiple revisions of the Basic Parameter Table they may do so provided the table headers are in order starting with the oldest version. The total number of parameter headers is specified in the NPH field of the SFDP header, see 6.2. All subsequent parameter headers need to be contiguous and may be specified by JEDEC or by vendors using the same structure (shown in Figure 4). Minor revisions may overlap earlier revisions by starting at the same address as an earlier revision but have additional length for parameters added in the later revision. This allows the use of legacy parameters without the need to repeat them in each new minor revision.

## 6.3.1 Parameter Header: 1st DWORD

| Bits  | Description                                                                                      |

|-------|--------------------------------------------------------------------------------------------------|

|       | Parameter Table Length                                                                           |

| 31:24 | This field specifies how many DWORDs are in the Parameter table.                                 |

|       | NOTE This field is 1's based. Therefore, 1 indicates 1 DWORD.                                    |

|       | Parameter Table Major Revision Number                                                            |

|       | This 8-bit field indicates the major revision number of the associated parameter table. The      |

|       | value in this field is 1 for tables defined by the JESD216A revision.                            |

| 23:16 |                                                                                                  |

|       | NOTE Major Revision starts at 01h. The Major Revision of JEDEC defined parameter tables can      |

|       | only be modified by updates to this standard. The Major Revision of a vendor-specified table is  |

|       | controlled by that vendor.                                                                       |

|       | Parameter Table Minor Revision Number                                                            |

|       | This 8-bit field indicates the minor revision number of the associated parameter table. The      |

|       | value in this field is 5 for tables defined by the JESD216A revision. The value in this field is |

| 15:8  | 0 for tables defined by the JESD216 initial release.                                             |

|       | NOTE Minor Revision starts at 00h. The Minor Revision of the JEDEC owned parameter tables can    |

|       | only be modified by updates to this standard. The Minor Revision of a vendor-specified table is  |

|       | controlled by that vendor.                                                                       |

|       | Parameter ID LSB:                                                                                |

| 7:0   | Refer to the paragraph below for the definition of this field.                                   |

|       | 15 11-1 p 11-10-11 11 11 11 11 11 11 11 11 11 11 11 11                                           |

# 6.3.2 Parameter Header: 2<sup>nd</sup> DWORD

| Bits  | Description                                                                                     |

|-------|-------------------------------------------------------------------------------------------------|

| 31:24 | Parameter ID MSB                                                                                |

| 31:24 | Refer to 6.3.2.1 for the definition of this field.                                              |

|       | Parameter Table Pointer (PTP)                                                                   |

| 23:0  | This 24-bit address specifies the start of this header's Parameter Table in the SFDP structure. |

|       | The address must be DWORD-aligned.                                                              |

## 6.3.2 Parameter Header: 2<sup>nd</sup> DWORD (cont'd)

#### 6.3.2.1 Definition of Parameter ID Field

The Parameter ID indicates the parameter table ownership and type.

The ID field is expanded to two bytes because a single byte is insufficient to uniquely identify all manufacturers (potential owners). For example, in JEP106 the Manufacturer's Identification Code of 2Ch is shared by Micron, Celestica, Tachyon Semiconductor, etc. The Bank Number uniquely associates the 2Ch code with a single manufacturer. Micron is on Bank one, Celestica is on Bank two, and Tachyon Semiconductor is on Bank three. In the SFDP headers, when a Manufacturer's Identification Code is stored in the Parameter ID Least Significant Byte (LSB) the Bank number is stored in the Parameter ID Most Significant Byte (MSB).

JEP106 Manufacturer's Identification Code is an eight (8) bit field, consisting of seven (7) data bits plus one (1) odd parity bit. In SFDP headers, a Parameter ID LSB with odd parity signifies a Manufacturer's Identification Code and a Parameter ID LSB with even parity signifies a Function Specific table.

Parameter IDs with an MSB of:

- FFh through 80h are defined by the JEDEC 42.4 committee

- 7Fh though 01h identify the bank number of a JEDEC JEP106 assigned Manufacturer ID.

- 00h is reserved because JEP106 bank numbering begins at 01h

Parameter IDs with an MSB of FFh through 80h use the LSB to identify the Function Specific table type:

- Any parameter ID with LSB 00h identifies the SPI protocol Basic Parameter Table.

- LSB values with even parity are Function Specific tables that are defined by the JC-42.4 committee.

- LSB values with odd parity are illegal to prevent any confusion with JEP106 manufacturer ID values.

The Parameter ID LSB value of 00h is reserved for the Basic Parameter Table defined by this standard. For backwards compatibility the MSB is FFh when the LSB is 00h and LSB 00h shall not be used when the MSB is any value other than FFh. This is because some legacy systems using the original JESD216 may ignore the MSB and assume any parameter ID with LSB of 00h is the Basic Parameter Table.

Function Specific tables may be defined by the JC-42.4 Committee, a manufacturer, or third-party. The purpose of the Function Specific tables is to allow development of features and associated parameter tables common to multiple manufacturers, prior to the parameter tables being incorporated into the next revision of JESD216. Allocation of IDs for Function Specific tables is requested through the JEDEC office, see Annex B.

Parameter IDs with an MSB of 7Fh though 01h use the LSB to identify the JEDEC JEP106 assigned Manufacturer ID within the designated bank. The identified manufacturer owns the definition of the parameter table. The parameter table structure is vendor specific.

## 6.3.3 Example of an SFDP Header

Figure 5 shows an example of an SFDP Header with SFDP Revision 1.0, one Parameter Header, Parameter Table length of 9 DWORDs, 1<sup>st</sup> Parameter Header Revision 1.0, JEDEC ID of 00h, and the Parameter Table Pointer pointing to location 000010h.

|               | [31:24] | [23:16] | [15:8] | [7:0] | Hex Byte<br>Location |

|---------------|---------|---------|--------|-------|----------------------|

| SFDP          | 50h     | 44h     | 46h    | 53h   | <[3h:0h]             |

| Header        | FFh     | 00h     | 01h    | 00h   | < [7h:4h]            |

| 1st Parameter | 09h     | 01h     | 00h    | 00h   | < [Bh:8h]            |

| Header        | FFh     | 00h     | 00h    | 10h   | < [Fh:Ch]            |

Figure 5 — Example of an SFDP Header

#### **6.4 JEDEC Basic Flash Parameter Table**

Parameter tables contain coded information describing the features and capabilities of the serial flash. The first parameter table as defined by JEDEC is mandatory and its starting address is specified by the PTP field of the 1<sup>st</sup> Parameter Header. This table identifies some of the basic features of SPI protocol flash memory devices.

| DWORD | Description                                                                         |  |

|-------|-------------------------------------------------------------------------------------|--|

| 1     | Uniform 4KB Sectors, Write Buffer Size, Volatile Status Register, Fast Read Support |  |

|       | (1-1-2) (1-2-2) (1-4-4)(1-1-4), Number of Address Bytes, DTR Support                |  |

| 2     | Memory Density                                                                      |  |

| 3     | Fast Read (1-4-4) (1-1-4): Wait States, Mode Bit Clocks, Instruction                |  |

| 4     | Fast Read (1-1-2) (1-2-2): Wait States, Mode Bit Clocks, Instruction                |  |

| 5     | Fast Read (2-2-2) (4-4-4) Support                                                   |  |

| 6     | Fast Read (2-2-2): Wait States, Mode Bit Clocks, Instruction                        |  |

| 7     | Fast Read (4-4-4): Wait States, Mode Bit Clocks, Instruction                        |  |

| 8     | Sector Type 1 & 2 Size and Instruction                                              |  |

| 9     | Sector Type 3 & 4 Size and Instruction                                              |  |

| 10    | Sector Type (1:4) Typical Erase Times and Multiplier Used To Derive Max Erase Times |  |

| 11    | Chip Erase Typical Time, Byte Program and Page Program Typical Times, Page Size     |  |

| 12    | Erase/Program Suspend/Resume Support, Intervals, Latency, Keep Out Area Size        |  |

| 13    | Program/Erase Suspend/Resume Instructions                                           |  |

| 14    | Deep Powerdown and Status Register Polling Device Busy                              |  |

| 15    | Hold and WP Disable Function, Quad Enable Requirements, 4-4-4 Mode Enable/Disable   |  |

|       | Sequences, 0-4-4 Entry/Exit Methods and Support                                     |  |

| 16    | 32-bit Address Entry/Exit Methods and Support, Soft Reset and Rescue Sequences,     |  |

|       | Volatile and Nonvolatile Status Register Support                                    |  |

# **6.4.1 JEDEC Basic Flash Parameter Table:** 1<sup>st</sup> **DWORD**

| Bits  | Description                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------|

| 31:23 | Unused                                                                                                              |

| 31.23 | Contains FFh and can never be changed.                                                                              |

|       | Supports (1-1-4) Fast Read  Davide symmetric single input instruction & address and avail output data Fast Read     |

| 22    | Device supports single input instruction & address and quad output data Fast Read.                                  |

|       | 0: (1-1-4) Fast Read NOT supported.                                                                                 |

|       | 1: (1-1-4) Fast Read supported.                                                                                     |

|       | Supports (1-4-4) Fast Read                                                                                          |

|       | Device supports single input instruction, quad input address, and quad output data Fast                             |

| 21    | Read.                                                                                                               |

|       | 0: (1-4-4) Fast Read NOT supported.                                                                                 |

|       | 1: (1-4-4) Fast Read supported.                                                                                     |

|       | Supports (1-2-2) Fast Read                                                                                          |

|       | Device supports single input instruction, dual input address, and dual output data Fast                             |

| 20    | Read.                                                                                                               |

|       | 0: (1-2-2) Fast Read NOT supported.                                                                                 |

|       | 1: (1-2-2) Fast Read supported.                                                                                     |

|       | Supports Double Transfer Rate (DTR) Clocking                                                                        |

|       | Indicates the device supports some type of double transfer rate clocking.                                           |

| 19    | O. DTD NOT comported                                                                                                |

|       | 0: DTR NOT supported 1: DTR Clocking supported                                                                      |

|       |                                                                                                                     |

|       | Address Bytes Number of bytes used in addressing flash array read, write and erase:                                 |

|       | 00b: 3-Byte only addressing                                                                                         |

|       | 01b: 3- or 4-Byte addressing (e.g., defaults to 3-Byte mode; enters 4-Byte mode on                                  |

|       | command)                                                                                                            |

| 18:17 | 10b: 4-Byte only addressing                                                                                         |

|       | 11b: Reserved                                                                                                       |

|       | NOTE This field refers to the number of address bits/bytes that are clocked in for any command                      |

|       | requiring an address except for SFDP Header or Table accesses. All SFDP accesses use 3-byte                         |

|       | addressing. Examples: Read, Fast Read, Write, 4 kilobyte Erase.                                                     |

|       | · · · · · · · · · · · · · · · · · · ·                                                                               |

|       | Supports (1-1-2) Fast Read Device supports single input instruction & address and dual output data Fast Read with 8 |

|       | wait states.                                                                                                        |

| 16    |                                                                                                                     |

|       | 0: (1-1-2) Fast Read NOT supported.                                                                                 |

|       | 1: (1-1-2) Fast Read supported.                                                                                     |

|       | 4 Kilobyte Erase Instruction                                                                                        |

| 15:8  | NOTE If 4 kilobyte erase is not supported, then enter FFh. This instruction must also be included                   |

|       | in one of the Sector Types in 6.4.8 or 6.4.9.                                                                       |

| Bits | Description                                                                                                                                                                                                                                          |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Unused                                                                                                                                                                                                                                               |

| 7:5  | Contains 111b and can never be changed.                                                                                                                                                                                                              |

|      | Write Enable Instruction Select for Writing to Volatile Status Register                                                                                                                                                                              |

|      | This bit only applies if bit 3 is 1.                                                                                                                                                                                                                 |

|      | <ul> <li>0: flash device requires instruction 50h as the write enable prior to performing a volatile write to the status register</li> <li>1: flash device requires instruction 06h as the write enable prior to performing a volatile</li> </ul>    |

| 4    | write to the status register.                                                                                                                                                                                                                        |

|      | NOTE If target flash status register is nonvolatile, then bits 3 and 4 must be set to 00b.                                                                                                                                                           |

|      | This bit definition is maintained for legacy compatibility only. New system implementations should refer to 6.4.16 for a full definition of volatile and non-volatile behavior.                                                                      |

|      | Volatile Status Register Block Protect bits                                                                                                                                                                                                          |

| 3    | 0: Block Protect bits in device's status register are solely non-volatile or may be programmed either as volatile using the 50h instruction for write enable or non-volatile using the 06h instruction for write enable.                             |

| 3    | 1: Block Protect bits in device's status register are solely volatile.                                                                                                                                                                               |

|      | NOTE If target flash register is nonvolatile, then bits 3 and 4 must be set to 00b. This bit definition is maintained for legacy compatibility only. New devices should refer to 6.4.16 for a full definition of volatile and non-volatile behavior. |

|      | Write Granularity                                                                                                                                                                                                                                    |

|      | 0: 1 Byte – Use this setting for single byte programmable devices or buffer programmable devices when the buffer is less than 64 bytes (32 Words).                                                                                                   |

| 2    | 1: Use this setting for buffer programmable devices when the buffer size is 64 bytes (32 Words) or larger.                                                                                                                                           |

|      | This bit definition is maintained for legacy compatibility only. New system implementations should refer to 6.4.11for the buffer (page) size. The legacy minimum write granularity is a single byte within any size programming buffer.              |

|      | Block/Sector Erase Sizes                                                                                                                                                                                                                             |

|      | Identifies if the device supports uniform 4k erase blocks. This erase size information must also be included one of the Sector Types in 6.4.8 or 6.4.9.                                                                                              |

|      | 00b: Reserved                                                                                                                                                                                                                                        |

| 1:0  | 01b: 4 kilobyte Erase is supported throughout the device                                                                                                                                                                                             |

|      | 10b: Reserved                                                                                                                                                                                                                                        |

|      | 11b: Use this setting only if uniform 4 kilobyte erase is unavailable.                                                                                                                                                                               |

|      | NOTE This is a legacy field. Refer to sections 6.4.8 and 6.4.9 for information on what sector sizes are supported.                                                                                                                                   |

# **6.4.2** JEDEC Basic Flash Parameter Table: 2<sup>nd</sup> DWORD

| Bits | Description                                                                                                                                            |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Flash Memory Density                                                                                                                                   |

|      | For densities 2 gigabits or less, bit-31 is set to 0b. The field 30:0 defines the size in bits.                                                        |

|      | Example: 00FFFFFh = 16 megabits                                                                                                                        |

| 31:0 |                                                                                                                                                        |

|      | For densities 4 gigabits and above, bit-31 is set to 1b. The field 30:0 defines 'N' where the density is computed as $2^N$ bits (N must be $\ge 32$ ). |

|      | Example: $80000021h = 2^33 = 8$ gigabits                                                                                                               |

## 6.4.3 JEDEC Basic Flash Parameter Table: 3<sup>rd</sup> DWORD

| 6.4.3 JE | 5.4.3 JEDEC Basic Flash Parameter Table: 3 <sup>rd</sup> DWORD                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bits     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 31:24    | (1-1-4) Fast Read Instruction Instruction for single input instruction & address and quad output data Fast Read.                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 23:21    | (1-1-4) Fast Read Number of Mode Clocks This field will be 000b if Mode Bits are not supported,  NOTE This field should be counted in clocks not number of bits received by the serial flash. The master drives the bus during "mode bits" cycles; the master tri-states the bus during "dummy" cycles.  Example: If 4 mode bits are needed with a single input address phase command, this field would be 100b.                              |  |  |  |

| 20:16    | (1-1-4) Fast Read Number of Wait states (dummy clocks) needed before valid output This field will be 00000b if wait states/dummy clocks are not supported. (The number of dummy clocks should be > 0 to avoid contention on bi-directional pins.)  Example: If 8 bits are needed with a single input address phase command, this field would be 01000b.                                                                                       |  |  |  |

| 15:8     | (1-4-4) Fast Read Instruction Instruction for single input instruction, quad input address, and quad output data Fast Read.                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 7:5      | Quad Input Address Quad Output (1-4-4) Fast Read Number of Mode Clocks This field will be 000b if Mode bits are not supported,  NOTE This field should be counted in clocks not number of bits received by the serial flash. The master drives the bus during "mode bits" cycles; the master tri-states the bus during "dummy" cycles.  Example: If 8 mode bits are needed with a quad input address phase command, this field would be 010b. |  |  |  |

| 4:0      | (1-4-4) Fast Read Number of Wait states (dummy clocks) needed before valid output This field will be 00000b if wait states/dummy clocks are not supported. (The number of dummy clocks should be > 0 to avoid contention on bi-directional pins.)  Example: If 16 bits are needed with a quad input address phase command, this field would be 00100b.                                                                                        |  |  |  |

# **6.4.4 JEDEC Basic Flash Parameter Table: 4<sup>th</sup> DWORD**

| Bits  | Description                                                                                                                                                                                            |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | (1-2-2) Fast Read Instruction Instruction for single input instruction, dual input address, and dual output data Fast Read.                                                                            |

|       | (1-2-2) Fast Read Number of Mode Clocks                                                                                                                                                                |

|       | This field will be 000b if Mode bits are not supported,                                                                                                                                                |

| 23:21 | NOTE This field should be counted in clocks not number of bits received by the serial flash. The master drives the bus during "mode bits" cycles; the master tri-states the bus during "dummy" cycles. |

|       | <b>Example:</b> If 8 mode bits are needed with a dual input address phase command, this field would be 100b.                                                                                           |

|       | (1-2-2) Fast Read Number of Wait states (dummy clocks) needed before valid output                                                                                                                      |

|       | This field will be 00000b if wait states/dummy clocks are not supported.                                                                                                                               |

| 20:16 | (The number of dummy clocks should be > 0 to avoid contention on bi-directional pins.)                                                                                                                 |

|       | <b>Example:</b> If 8 bits are needed with a dual input address phase command, this field would be 00100b.                                                                                              |

| 15:8  | (1-1-2) Fast Read Instruction Instruction for single input instruction& address and dual output data Fast Read. Note: The industry standard is 3Bh                                                     |

|       | (1-1-2) Fast Read Number of Mode Clocks                                                                                                                                                                |

|       | This field will be 000b if Mode bits are not supported,                                                                                                                                                |

| 7:5   | NOTE This field should be counted in clocks not number of bits received by the serial flash.                                                                                                           |

|       | <b>Example:</b> If 4 mode bits are needed with a single input address phase command, this field would be 100b.                                                                                         |

|       | (1-1-2) Fast Read Number of Wait states (dummy clocks) needed before valid output                                                                                                                      |

|       | This field should be programmed with 01000b for 8 clocks of dummy cycle.                                                                                                                               |

| 4:0   | (The number of dummy clocks should be > 0 to avoid contention on bi-directional pins.)                                                                                                                 |

|       | NOTE For legacy reasons, if dummy clocks for this instruction is not 01000b, then bit 16 in 6.4.1 (Supports (1-1-2) Fast Read with 8 wait states) must NOT be set to '1'.                              |

# **6.4.5** JEDEC Basic Flash Parameter Table: 5<sup>th</sup> DWORD

| Bits | Description                                                                      |

|------|----------------------------------------------------------------------------------|

| 31:5 | Reserved. These bits default to all 1's                                          |

|      | Supports (4-4-4) Fast Read                                                       |

|      | Device supports Quad input instruction & address and quad output data Fast Read. |

| 4    |                                                                                  |

|      | 0: (4-4-4) Fast Read NOT supported.                                              |

|      | 1: (4-4-4) Fast Read supported.                                                  |

| 3:1  | Reserved. These bits default to all 1's                                          |

|      | Supports (2-2-2) Fast Read                                                       |

|      | Device supports dual input instruction& address and dual output data Fast Read.  |

| 0    |                                                                                  |

|      | 0: (2-2-2) Fast Read NOT supported.                                              |

|      | 1: (2-2-2) Fast Read supported.                                                  |

## 6.4.6 JEDEC Basic Flash Parameter Table: 6<sup>th</sup> DWORD

| Bits  | Description                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | (2-2-2) Fast Read Instruction Instruction for dual input instruction& address and dual output data Fast Read.                                                                                                                                                                                                                                                                                            |

| 23:21 | (2-2-2) Fast Read Number of Mode Clocks  This field will be 000b if Mode bits are not supported,  NOTE This field should be counted in clocks not number of bits received by the serial flash. The master drives the bus during "mode bits" cycles; the master tri-states the bus during "dummy" cycles.  Example: If 4 mode bits are needed with a (2-2-2) Fast Read command, this field would be 010b. |

| 20:16 | (2-2-2) Fast Read Number of Wait states (dummy clocks) needed before valid output This field will be 00000b if wait states/dummy clocks are not supported. (The number of dummy clocks should be > 0 to avoid contention on bi-directional pins.)  Example: If 8 bits are needed with a (2-2-2) Fast Read command, this field would be 00100b.                                                           |

| 15:0  | Reserved. These bits default to all 1's                                                                                                                                                                                                                                                                                                                                                                  |

# **6.4.7 JEDEC Basic Flash Parameter Table: 7**<sup>th</sup> **DWORD**

| Bits  | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | (4-4-4) Fast Read Instruction Instruction for quad input instruction/address, quad output data Fast Read.                                                                                                                                                                                                                                                                                                     |

| 23:21 | (4-4-4) Fast Read Number of Mode Clocks This field will be 000b if Mode bits are not supported,  NOTE This field should be counted in clocks not number of bits received by the serial flash. The master drives the bus during "mode bits" cycles; the master tri-states the bus during "dummy" cycles.  Example: If 8 mode bits are needed with a (4-4-4) Fast Read phase command, this field would be 010b. |

| 20:16 | (4-4-4) Fast Read Number of Wait states (dummy clocks) needed before valid output This field will be 00000b if wait states/dummy clocks are not supported. (The number of dummy clocks should be > 0 to avoid contention on bi-directional pins.)  Example: If 16 bits are needed with a (4-4-4) Fast Read phase command, this field would be 00100b.                                                         |

| 15:0  | Reserved. These bits default to all 1's                                                                                                                                                                                                                                                                                                                                                                       |

# 6.4.8 JEDEC Basic Flash Parameter Table: 8th DWORD

NOTE If the device uses a 4k subsector size, that size and instruction must be included somewhere in DWORDs 8 or 9. This allows the user to discover the typical and maximum erase times for the 4k subsector by referencing DWORD 10.

| Bits  | Description                                                                                 |

|-------|---------------------------------------------------------------------------------------------|

| 31:24 | Sector Type 2 Instruction                                                                   |

| 31.24 | Instruction used to erase the number of bytes specified by Sector Type 2 Size (bits 23-16). |

|       | Sector Type 2 Size:                                                                         |

|       | This field will be 00h if this sector type does not exist.                                  |

| 23:16 | NOTE This field specifies 'N' and is used to calculate sector/block size = 2^N bytes        |

|       | <b>Example:</b> If the sector size is 32 kilobytes, this field would 0Fh.                   |

| 15.0  | Sector Type 1 Instruction                                                                   |

| 15:8  | Instruction used to erase the number of bytes specified by Sector Type 1 Size (bits 7-0).   |

|       | Sector Type 1 Size                                                                          |

| 7:0   | NOTE This field specifies 'N' and is used to calculate sector/block size = 2^N bytes        |

|       | <b>Example:</b> If the sector size is 4 kilobytes, this field would 0Ch.                    |

# **6.4.9 JEDEC Basic Flash Parameter Table:** 9<sup>th</sup> **DWORD**

| Bits  | Description                                                                                 |

|-------|---------------------------------------------------------------------------------------------|

| 31:24 | Sector Type 4 Instruction                                                                   |

|       | Instruction used to erase the number of bytes specified by Sector Type 4 Size (bits 23-16). |

|       | Sector Type 4 Size                                                                          |

|       | This field will be 00h if this sector type does not exist.                                  |

| 23:16 | NOTE This field specifies 'N' and is used to calculate sector/block size = 2^N bytes        |

|       | <b>Example:</b> If the sector size is 256 kilobytes, this field would 12h.                  |

| 15:8  | Sector Type 3 Instruction                                                                   |

| 13.0  | Instruction used to erase the number of bytes specified by Sector Type 3 Size (bits 7-0).   |

|       | Sector Type 3 Size                                                                          |

|       | This field will be 00h if this sector type does not exist.                                  |

| 7:0   | NOTE This field specifies 'N' and is used to calculate sector/block size = 2^N bytes        |

|       | <b>Example:</b> If the sector size is 64 kilobytes, this field would 10h.                   |

|       |                                                                                             |

# **6.4.10** JEDEC Basic Flash Parameter Table: 10<sup>th</sup> DWORD

| Bits  | Description                                                                                                                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:25 | Sector Type 4 Erase, Typical time                                                                                                                                                                                                   |

|       | Time the device <i>typically</i> takes to erase a sector of Type 4 size, see 6.4.9. User must poll device busy to determine if the operation has completed. This field has no meaning if the Sector Type 4 size is 00h.             |

|       | 31:30 units (00b: 1 ms, 01b: 16 ms, 10b: 128 ms, 11b: 1 s) 29:25 count                                                                                                                                                              |

|       | Formula: typical time = $(count + 1)*units$                                                                                                                                                                                         |

|       | Example: If count=2 and units=10b, then typical time is $(2+1)*128ms = 384 ms$<br>The range is 1ms to 32 seconds in four groups: 1 ms to 32 ms, 16 ms to 512 ms, 128 ms to 4096 ms, 1 s to 32 s                                     |

|       | Sector Type 3 Erase, Typical time                                                                                                                                                                                                   |

| 24:18 | Time the device <i>typically</i> takes to erase a sector of Type 3 size, see 6.4.9. User must poll device busy to determine if the operation has completed. This field has no meaning if the Sector Type 3 size is 00h.             |

|       | 24:23 units (00b: 1 ms, 01b: 16 ms, 10b: 128 ms, 11b: 1 s) 22:18 count                                                                                                                                                              |

|       | Formula: typical time = $(count + 1)*units$                                                                                                                                                                                         |

|       | Example: If count=1 and units=10b, then typical time is $(1+1)*128ms = 256 ms$<br>The range is 1ms to 32 seconds in four groups: 1 ms to 32 ms, 16 ms to 512 ms, 128 ms to 4096 ms, 1 s to 32 s                                     |

|       | Sector Type 2 Erase, Typical time                                                                                                                                                                                                   |

| 17:11 | Time the device <i>typically</i> takes to erase a sector of Type 2 size, see 6.4.8. User must poll device busy to determine if the operation has completed. This field has no meaning if the corresponding Sector Type size is 00h. |

|       | 17:16 units (00b: 1 ms, 01b: 16 ms, 10b: 128 ms, 11b: 1 s) 15:11 count                                                                                                                                                              |

|       | Formula: typical time = $(count + 1)*units$                                                                                                                                                                                         |

|       | Example: If count=0 and units=10b, then typical time is $(0+1)*128ms = 128 ms$<br>The range is 1ms to 32 seconds in four groups: 1 ms to 32 ms, 16 ms to 512 ms, 128 ms to 4096 ms, 1 s to 32 s                                     |

|      | Sector Type 1 Erase, Typical time                                                                                                                                                                                                                                                                                 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10:4 | Time the device <i>typically</i> takes to erase a sector of Type 1 size, see 6.4.8. User must poll device busy to determine if the operation has completed. This field has no meaning if the corresponding Sector Type size is 00h.                                                                               |

|      | 10:9 units (00b: 1 ms, 01b: 16 ms, 10b: 128 ms, 11b: 1 s)<br>8:4 count                                                                                                                                                                                                                                            |

|      | Formula: typical time = $(count + 1)*units$                                                                                                                                                                                                                                                                       |

|      | Example: If count=1 and units=10b, then typical time is 1*128ms = 128 ms<br>The range is 1ms to 32 seconds in four groups: 1 ms to 32 ms, 16 ms to 512 ms, 128 ms to 4096 ms, 1 s to 32 s                                                                                                                         |

|      | Multiplier from typical erase time to maximum erase time                                                                                                                                                                                                                                                          |

|      | 3:0 count                                                                                                                                                                                                                                                                                                         |

| 3:0  | Formula: Sector Type n (or Chip) erase maximum time = 2 * (count + 1) * Sector Type n (or Chip) erase typical time                                                                                                                                                                                                |

|      | Example: If count = 9, then Sector Type n (or Chip) erase maximum time is 20 * Sector Type n (or Chip) erase typical time                                                                                                                                                                                         |

|      | NOTE 1 'n' = 1, 2, 3, or 4                                                                                                                                                                                                                                                                                        |

|      | NOTE 2 This multiplier applies to all sector erases and the chip erase. The maximum time is intended to be used as a watchdog timeout for an error or failure condition. Since a common scale factor is used across all erase sizes, any particular maximum time may only approximate the datasheet maximum time. |

# **6.4.11 JEDEC Basic Flash Parameter Table:** 11<sup>th</sup> DWORD

| Bits  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 30:24 | Chip Erase, Typical time Typical time to erase the entire device. User must poll device busy to determine if the operation has completed.  30:29 units (00b: 16 ms, 01b: 256 ms, 10b: 4 s, 11b: 64 s) 28:24 count  Formula: typical time = (count + 1)*units  Example: If count=5 and units=10b, then typical time is: 5*4 s = 20 s The range of this field is 16ms to 2048 seconds in four groups: 16 ms to 512 ms, 256 ms to 8192 ms, 4 s to 128 s, 64 s to 2048 s                                                                                                                                                                                                                                                                                                            |

| 23:19 | Byte Program Typical time, additional byte  Time the device <i>typically</i> takes to write each additional byte after the first. User must poll device busy to determine if the operation has completed.  23 units (0: 1 us, 1: 8 us)  22:19 count  Formula: additional byte time = (count + 1)*units/byte  Example: If units = 1 and count =4, then each additional byte typically adds  (4+1)*8 us = 40 us to the programming time. For 16 bytes, the additional time would be 16 * 40 us = 640 us  The range is 1 us to 128 us in two groups: 1 us to 16 us and 8 us to 128 us.  NOTE The programming time for small numbers of bytes does not scale linearly up to a full page programming time. When the number of bytes being programmed exceeds ½ of a page size, users |

| 18:14 | should base estimates on the Page Program typical time in this DWORD.  Byte Program Typical time, first byte  Time the device <i>typically</i> takes to write the first byte in a sequence. User must poll device busy to determine if the operation has completed.  18 units (0: 1 us, 1: 8 us)  17:14 count  Formula: first byte typical time = (count + 1)*units  Example: If units = 0 and count = 7, then typical time is (7+1)*1 us = 8 us  The range is 1 us to 128 us in two groups: 1 us to 16 us and 8 us to 128 us                                                                                                                                                                                                                                                   |